Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

8-12

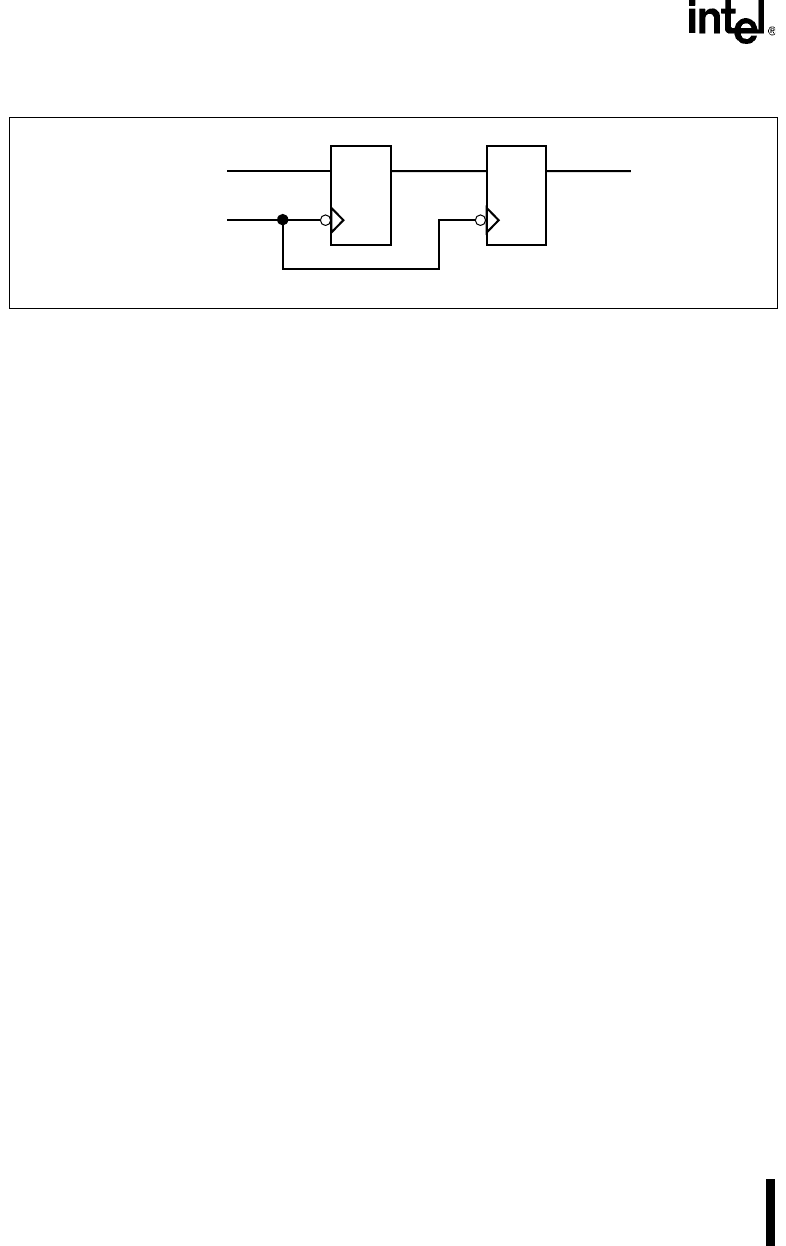

Figure 8-8. Reset Synchronization Circuit

8.4.2 Power-up Considerations

8.4.2.1 Built-in Self Test

The Intel386 EX processor supports the Intel386 SX processor built-in self-test (BIST) mode for

testing core functions. To initiate the self test, follow these steps:

1. Hold the RESET pin high for a minimum of 80 CLK2 cycles.

2. Transition the RESET pin from high to low while keeping the BUSY# pin asserted. The

BUSY# input should be asserted at least eight CLK2 cycles before the falling edge of

RESET and must be kept asserted for at least eight CLK2 cycles after the falling edge of

RESET.

Once BIST has been initiated, it takes approximately 2

20

processor clock cycles to complete. At

the completion of the BIST, the processor performs an internal reset and begins normal operation.

8.4.2.2 JTAG Reset

The processor supports an IEEE 1149.1 compliant JTAG boundary scan. The JTAG unit has its

own clock and RESET signals, independent from the rest of the processor. The processor requires

that the JTAG unit be reset before normal operation can begin. To reset the JTAG unit, invert the

processor RESET signal and connect this inverted RESET signal to the TRST# pin.

Synchronous

Reset Signal

to chip and

other system

logic.

DQ

CLK2

Asynchronous RESET

DQ

A2465-02