Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

16-6

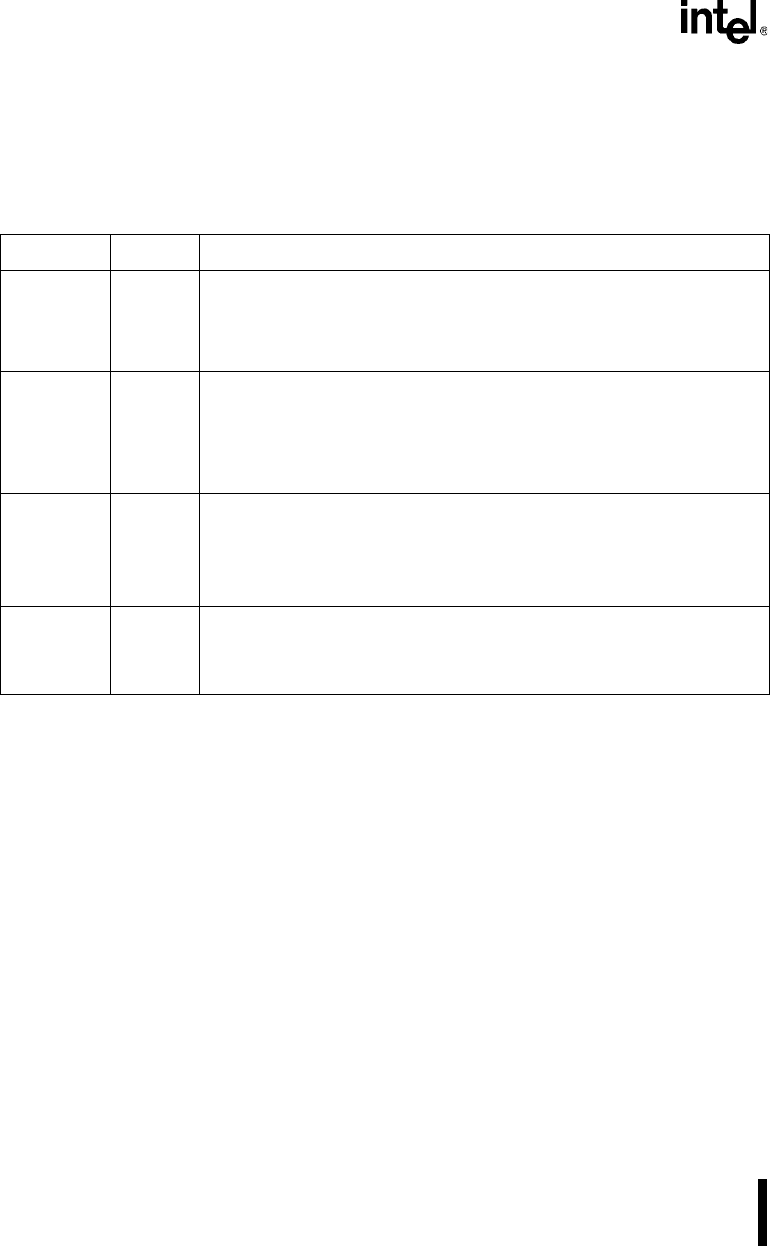

16.2 REGISTER DEFINITIONS

Each port has three control registers and a status register associated with it (Table 16-2). The con-

trol registers (PnCFG, PnDIR, and PnLTC) can be both read and written. The status register (Pn-

PIN) can only be read. All four registers reside in I/O address space.

Table 16-2. I/O Port Registers

Register Address Description

P1CFG

P2CFG

P3CFG

(read/write)

0F820H

0F822H

0F824H

Port

n

Mode Configuration:

Each bit controls the mode of the associated pin.

0 = Selects I/O mode.

1 = Selects peripheral mode.

P1DIR

P2DIR

P3DIR

(read/write)

0F864H

0F86CH

0F874H

Port

n

Direction:

Each bit controls the direction of a pin that is in I/O mode.

0 = Configures a pin as a complementary output. If a pin is in peripheral

mode, this value is ignored.

1 = Configures a pin as either an input or an open-drain output.

P1LTC

P2LTC

P3LTC

(read/write)

0F862H

0F86AH

0F872H

Port

n

Data Latch:

Each bit contains data to be driven onto an output pin that is in I/O mode. Write

the desired pin state value to this register. If a pin is in peripheral mode, this

value is ignored.

Reading this register returns the value in the register—not the actual pin state.

P1PIN

P2PIN

P3PIN

(read only)

0F860H

0F868H

0F870H

Port

n

Pin State:

Each bit of this read-only register reflects the state of the associated pin.

Reading this register returns the current pin state value, regardless of the pin’s

mode and direction.