11-9

ASYNCHRONOUS SERIAL I/O UNIT

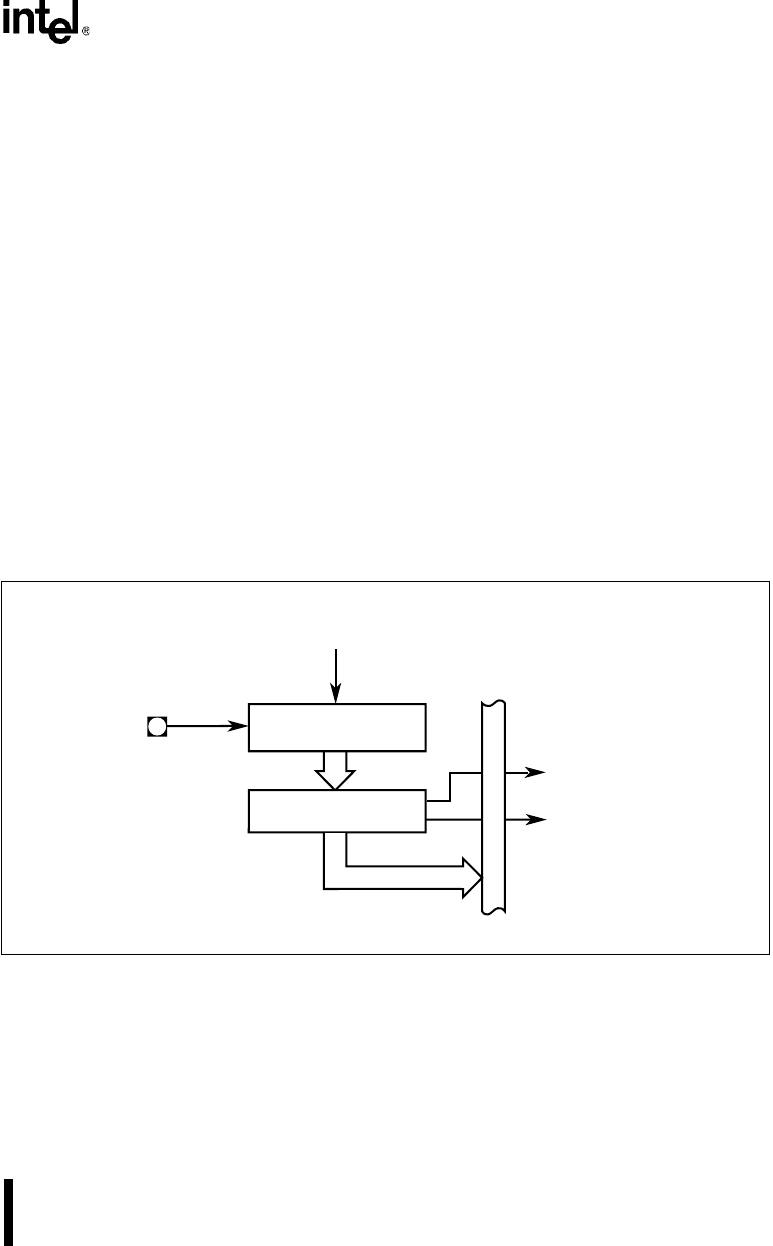

11.2.3 SIO

n

Receiver

The data frame for receptions is programmable, and is identical to the data frame for transmis-

sions. It consists of a start bit, 5 to 8 data characters, an optional parity bit, and 1 to 2 stop bits.

The receiver can be programmed for even, odd, forced, or no parity. When the receiver detects a

parity condition other than what it was programmed for, it sets a parity error flag. In addition to

detecting parity errors, the receiver can detect break conditions, framing errors, and overrun er-

rors.

• A break condition indicates that the received data input is held in the spacing (logic 0) state

for longer than a data transmission time (the time of the start bit + data bits + parity + stop

bits).

• A framing error indicates that the received character did not have a valid stop bit.

• An overrun error indicates that new data overwrote old data before the old data was read.

Each SIO channel receiver contains a receive shift register, a receive buffer, and a receive data

pin (RXDn). Data received is shifted into the receive shift register via the RXDn pin. Once a data

byte has been received, the receiver strips off the asynchronous communication bits (start, stop,

and parity) and transfers the contents of its shift register to the receive buffer.

The RXD0 pin is multiplexed with another function. The pin configuration register (P2CFG) de-

termines whether the RXD0 signal or the alternate function is connected to the package pin.

Figure 11-5. SIO

n

Receiver

RXD

n

(pin mux)

Baud-rate

Clock

SIO

n

Receive Shift

Register

SIO

n

Receive Buffer

A2327-02

S

y

s

t

e

m

B

u

s

Receive Buffer Full

(To ICU and DMA)

Receiver Errors

(To ICU)