5-4 PPC405 Core User’s Manual

All asynchronous interrupt types can be masked. In addition, certain synchronous interrupt types can

be masked.

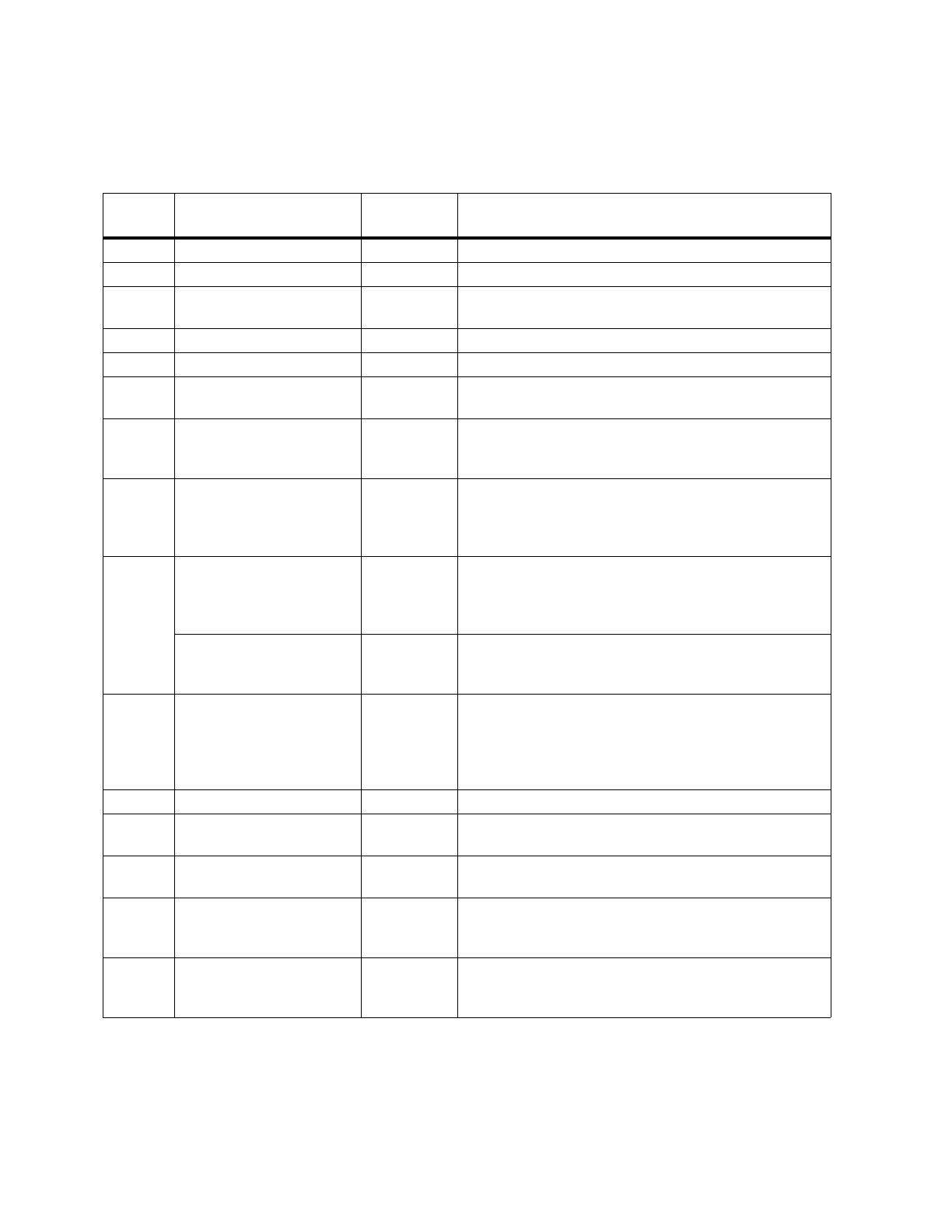

Table 5-1. Interrupt Handling Priorities

Priority Interrupt Type

Critical or

Noncritical Causing Conditions

1 Machine check—data Critical External bus error during data-side access

2 Debug—IAC Critical IAC debug event (in internal debug mode)

3 Machine check—

instruction

Critical Attempted execution of instruction for which an external

bus error occurred during fetch

4 Debug—EXC, UDE Critical EXC or UDE debug event (in internal debug mode)

5 Critical interrupt input Critical Active level on the critical interrupt input

6 Watchdog timer—first

time-out

Critical Posting of an enabled first time-out of the watchdog

timer in the TSR

7 Instruction TLB Miss Noncritical Attempted execution of an instruction at an address

and process ID for which a valid matching entry was not

found in the TLB

8 Instruction storage —

ZPR[Z

n

]=00

Noncritical Instruction translation is active, execution access to the

translated address is not permitted because

ZPR[Z

n

] = 00 in user mode, and an attempt is made to

execute the instruction

9 Instruction storage —

TLB_entry[EX] = 0

Noncritical Instruction translation is active, execution access to the

translated address is not permitted because

TLB_entry[EX] = 0, and an attempt is made to execute

the instruction

Instruction storage —

TLB_entry[G] = 1 or

SGR[G

n

]=1

Noncritical Instruction translation is active, the page is marked

guarded, and an attempt is made to execute the

instruction

Program Noncritical Attempted execution of illegal instructions, TRAP

instruction, privileged instruction in problem state, or

auxiliary processor (APU) instruction, or

unimplemented FPU instruction, or unimplemented

APU instruction, or APU interrupt, or FPU interrupt

System call Noncritical Execution of the sc instruction

APU Unavailable Noncritical Attempted execution of an APU instruction when

MSR[AP] = 0

FPU Unavailable Noncritical Attempted execution of an FPU instruction when

MSR[FP]=0.

11 Data TLB miss Noncritical Valid matching entry for the effective address and

process ID of an attempted data access is not found in

the TLB

12 Data storage—

ZPR[Z

n

]=00

Noncritical Data translation is active and data-side access to the

translated address is not permitted because

ZPR[Z

n

] = 00 in user mode