Debugging 8-17

comparison and by setting any bit combination in the DBCR1[DV1BE]. Each bit in DBCR1[DV1BE,

DV2BE] correspondes to a byte in DVC1 and DVC2. Exact address compare and range address

compare work the same for DVC as for a simple DAC.

DBSR[DR1] and DBSR[DW1] record status for DAC1 debug events. Which DBSR bit is set depends

on the setting of DBCR1[D1R] and DBCR[D1W]. If DBCR1[D1R] = 1, DBSR[DR1] = 1, assuming that

a DVC event occurred. Similarly, if DBCR1[D1W] = 1, DBSR[DW1] = 1, assuming that a DVC event

occurred.

Similarly, DBSR[DR2] and DBSR[DW2] record status for DAC2 debug events. Which DBSR bit is set

depends on the setting of DBCR1[D2R] and DBCR[D2W]. If DBCR1[D2R] = 1, DBSR[DR2] = 1,

assuming that a DVC event occurred. Similarly, if DBCR1[D2W] = 1, DBSR[DW2] = 1, assuming that

a DVC event occurred.

In the following example, a DVC1 event is enabled by setting DBCR1[D1R] = 1, DBCR1[D1W] = 1,

DBCR1[DA12] = 0, and DBCR1[DV1BE] = 0000. When the data address and data value match the

DAC1 and DVC1, a DVC1 event is recorded in DBSR[DR1] or DBSR[DW1], depending on whether

the operation is a load (read) or a store (write). This example corresponds to the last line of Table 8-3.

In Table 8-3,

n

is 1 or 2, depending on whether the bits apply to DAC1, DAC2, DVC1, and DVC2

events. “Hold” indicates that the DBSR holds its value unless cleared by software. “RA” indicates that

the operation is a read (load) and the data address compares (exact or range). “WA” indicates that the

operation is a write (store) and the data address compares (exact or range). “RV” indicates that the

operation is a read (load), the data address compares (exact or range), and the data value compares

according to DBCR1[DVC

n

].

The settings of DBCR1[DV1M] and DBCR1[DV2M] are more precisely defined in Table 8-5 and

Table 8-6. (

n

enables the table to apply to DBCR1[DV1M, DV2M] and DBCR1[DV1BE, DV2BE]).

DV

n

BE

m

indicates bytes selected (or not selected) for comparison in DBCR1[DV

n

BE].

When DBCR1[DV

n

M] = 01, the comparison is an AND; all bytes must compare to the appropriate

bytes of DVC1.

When DBCR1[DV

n

M] = 10, the comparison is an OR; at least one of the selected bytes must

compare to the appropriate bytes of DVC1.

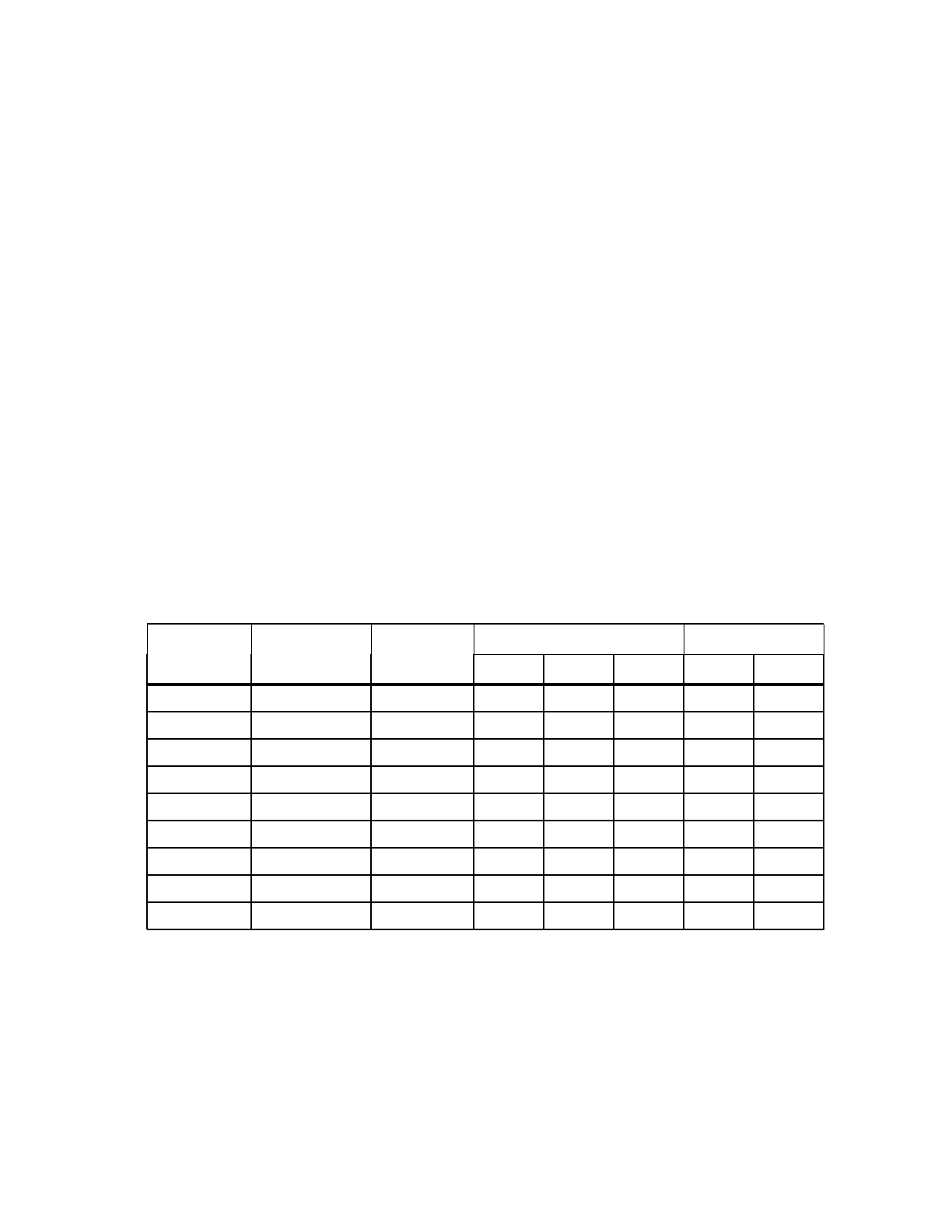

Table 8-3. Setting of DBSR Bits for DAC and DVC Events

DBCR1 DBSR

DACn Event DVCn Enabled DVCn Event [DnR] [DnW] [DA12] [DRn] [DWn]

0 — — — — — Hold Hold

— — — 0 0 — Hold Hold

1 0 — 0 1 — Hold WA

1 0 — 1 0 — RA Hold

10—11—RAWA

1 1 0 — — — Hold Hold

1 1 1 0 1 — Hold WV

1 1 1 1 0 — RV Hold

11111—RVWV