Instructions by Category B-9

B.4 Assembler Extended Mnemonics

In the appendix “Assembler Extended Mnemonics” of the PowerPC Architecture, it is required that a

PowerPC assembler support at least a minimal set of extended mnemonics. These mnemonics

encode to the opcodes of other instructions; the only benefit of extended mnemonics is improved

usability. Code using extended mnemonics can be easier to write and to understand. Table B-5 lists

the extended mnemonics required for the PPC405.

Note for every Branch Conditional mnemonic:

Bit 4 of the BO field provides a hint about the most likely outcome of a conditional branch. (“Branch

Prediction” on page 2-26 describes branch prediction). Assemblers should set BO

4

= 0 unless a

specific reason exists otherwise. In the BO field values specified in the following table, BO

4

= 0 has

always been assumed. The assembler must allow the programmer to specify branch prediction. To do

this, the assembler will support a suffix to every conditional branch mnemonic, as follows:

+ Predict branch to be taken.

– Predict branch not to be taken.

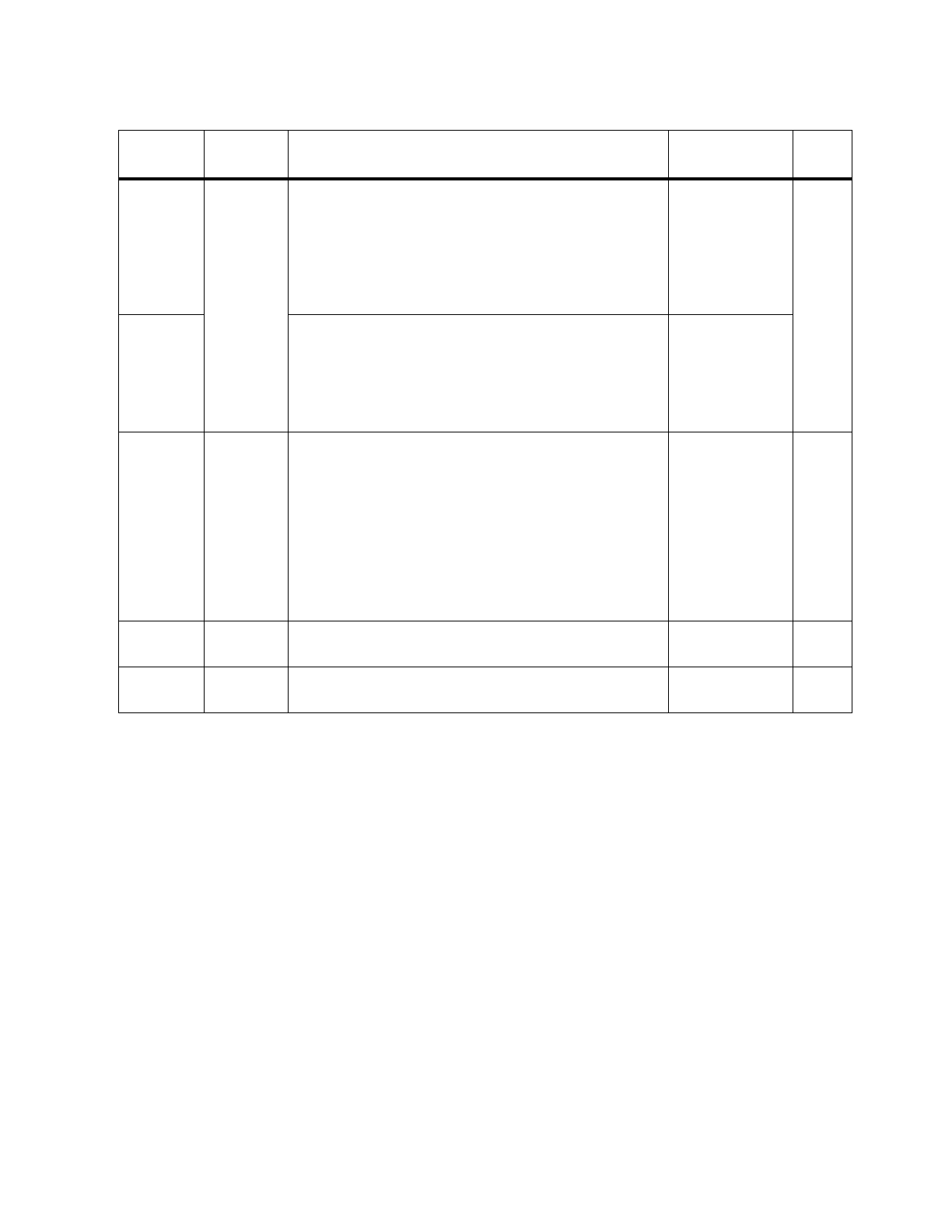

tlbsx RT,RA,RB Search the TLB array for a valid entry which translates

the EA

EA = (RA|0) + (RB).

If found,

(RT)

← Index of TLB entry.

If not found,

(RT) Undefined.

9-186

tlbsx. If found,

(RT)

← Index of TLB entry.

CR[CR0]

EQ

← 1.

If not found,

(RT) Undefined.

CR[CR0]

EQ

← 1.

CR[CR0]

LT,GT,SO

tlbwe RS,

RA,WS

If WS = 0:

Write TLBHI portion of the selected TLB entry from RS.

Write the TID field of the selected TLB entry from the

PID register.

TLBHI[(RA)]

← (RS)

TLB[(RA)]

TID

← (PID)

24:31

If WS = 1:

Write TLBLO portion of the selected TLB entry from RS.

TLBLO[(RA)]

← (RS)

9-188

wrtee RS Write value of RS

16

to the External Enable

bit (MSR[EE]).

9-196

wrteei E Write value of E to the External Enable

bit (MSR[EE]).

9-197

Table B-4. Privileged Instructions (continued)

Mnemonic Operands Function

Other Registers

Changed Page