Cache Operations 4-11

4.5 Cache Control and Debugging Features

Registers and instructions are provided to control cache operation and help debug cache problems.

For ICU debug, the icread instruction and the Instruction Cache Debug Data Register (ICDBDR) are

provided. See “ICU Debugging” on page 4-14 for more information. For DCU debug, the dcread

instruction is provided. See “DCU Debugging” on page 4-15 for more information.

CCR0 controls the behavior of the icread and the dcread instructions.

dcbz Data Cache Block Set to Zero

Fills a line in the cache with zeros and marks the line as modified.

If the line is not currently in the cache (and the address is marked as cachable and

non-write-through), the line is established, filled with zeros, and marked as modified

without actually filling the line from external memory. If the line is marked as either

non-cachable or write-through, an alignment exception results.

dccci Data Cache Congruence Class Invalidate

Invalidates a congruence class (both cache ways).

This is a privileged instruction.

dcread Data Cache Read

Reads either a data cache tag entry or a data word from a data cache line, typically

for debugging. Bits in CCR0 control instruction behavior (see “Cache Control and

Debugging Features” on page 4-11).

This is a privileged instruction.

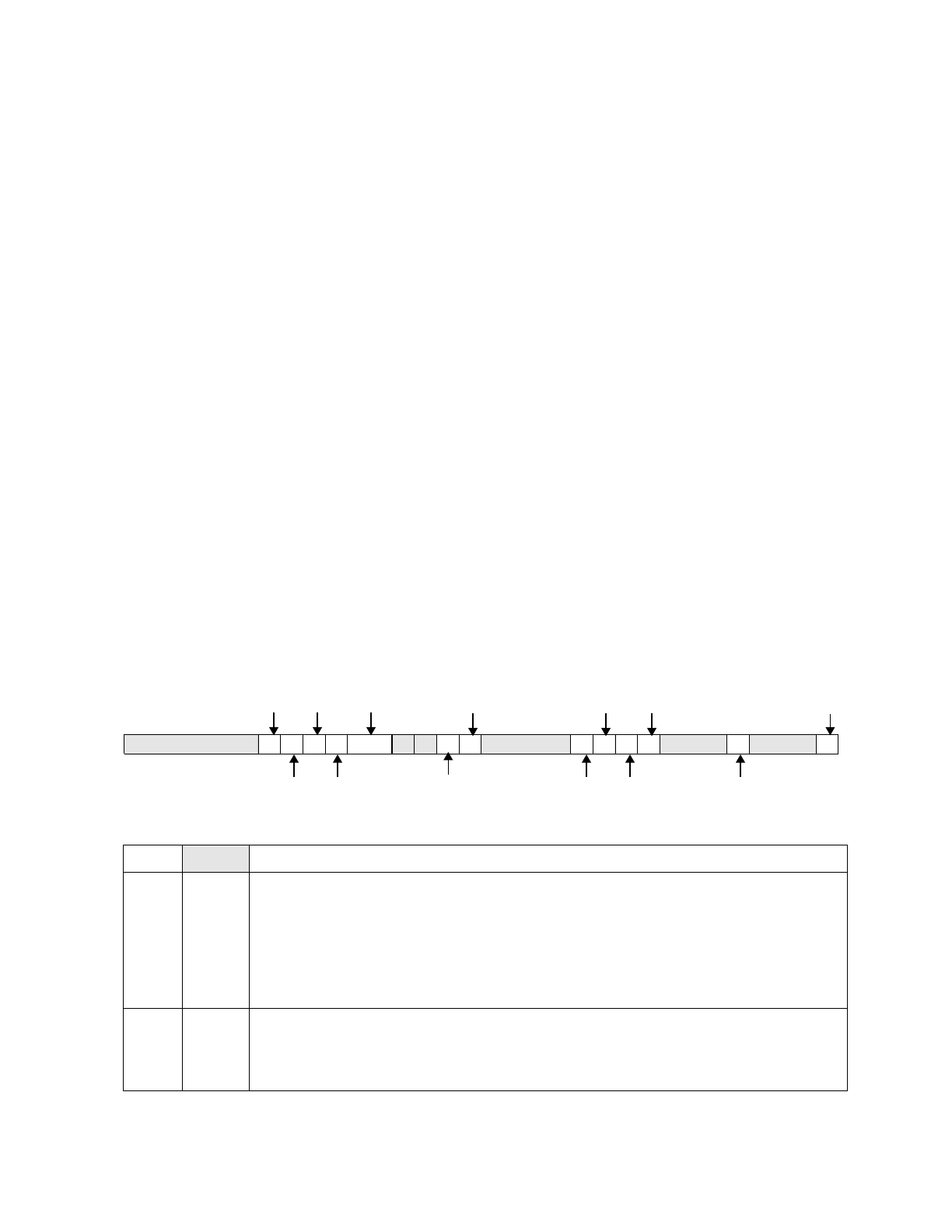

Figure 4-2. Core Configuration Register 0 (CCR0)

0:5 Reserved

6 LWL Load Word as Line

0 The DCU performs load misses or non-

cachable loads as words, halfwords, or

bytes, as requested

1 For load misses or non-cachable loads,

the DCU moves eight words (including

the target word) into the line fill buffer

7 LWOA Load Without Allocate

0 Load misses result in line fills

1 Load misses do not result in a line fill, but

in non-cachable loads

0 56789101112 13 14 15 16 19 20 21 22 23 24 26 27 28 30 31

CWS

CIS

LWL

LWOA

SWOA

U0XE

LBDE

PFC

PFNC FWOA

NCRSDPP1

IPP