5-10 PPC405 Core User’s Manual

The contents of SRR2 and SRR3 can be written to GPRs using the mfspr instruction. The contents of

GPRs can be written to SRR2 and SRR3 using the mtspr instruction.

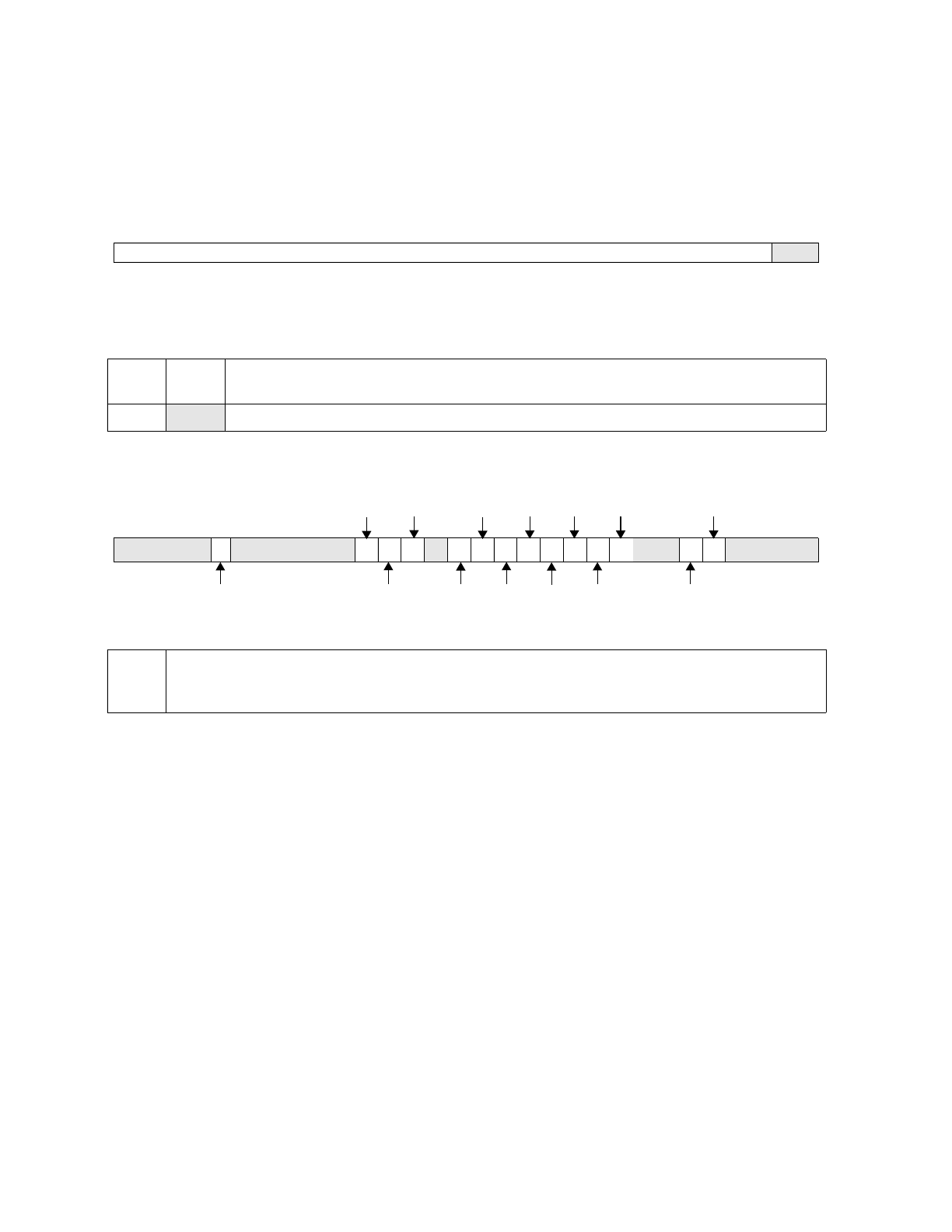

Figure 5-4 shows the bit definitions for SRR2.

.

Figure 5-5 shows the bit definitions for SRR3.

Because critical interrupts do not automatically clear MSR[ME], SRR2 and SRR3 can be corrupted by

a machine check interrupt, if the machine check occurs while SRR2 and SRR3 contain valid data that

has not yet been saved by the critical interrupt handler.

5.5.4 Exception Vector Prefix Register (EVPR)

The EVPR is a 32-bit register whose high-order 16 bits contain the prefix for the address of an

interrupt handling routine. The 16-bit interrupt vector offsets (shown in Table 5-2 on page 5-6) are

concatenated to the right of the high-order 16 bits of the EVPR to form the 32-bit address of an

interrupt handling routine.

The contents of the EVPR can be written to a GPR using the mfspr instruction. The contents of a

GPR can be written to EVPR using the mtspr instruction.

Figure 5-6 shows the EVPR bit definitions.

Figure 5-4. Save/Restore Register 2 (SRR2)

0:29 SRR2 receives an instruction address when a critical interrupt is taken; the Program

Counter is restored from SRR2 when rfci executes.

30:31

Reserved

Figure 5-5. Save/Restore Register 3 (SRR3)

0:31 SRR3 receives a copy of the MSR when a

critical interrupt is taken; the MSR is

restored from SRR3 when rfci executes.

0 29 30 31

0 567 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 31

DE

CE

EE

IR

WE

PR

DRME

FP

FE0

FE1

DWE

AP

APE