2-10 PPC405 Core User’s Manual

SPRG0–SPRG7 provide temporary storage locations. For example, an interrupt handler might save

the contents of a GPR to an SPRG, and later restore the GPR from it. This is faster than performing a

save/restore to memory. These registers are written by mtspr and read by mfspr.

Access to SPRG0–SPRG7 is privileged, except for read access to SPRG4–SPRG7. See “Privileged

SPRs” on page 2-32 for more information.

2.3.2.5 Processor Version Register (PVR)

The PVR is a read-only register that uniquely identifies a standard product or Core+ASIC

implementation. Software can examine the PVR to recognize implementation-dependent features and

determine available hardware resources.

Access to the PVR is privileged. See “Privileged SPRs” on page 2-32 for more information.

2.3.3 Condition Register (CR)

The CR contains eight 4-bit fields (CR0–CR7), as shown in Figure 3-8. The fields contain conditions

detected during the execution of integer or logical compare instructions, as indicated in the instruction

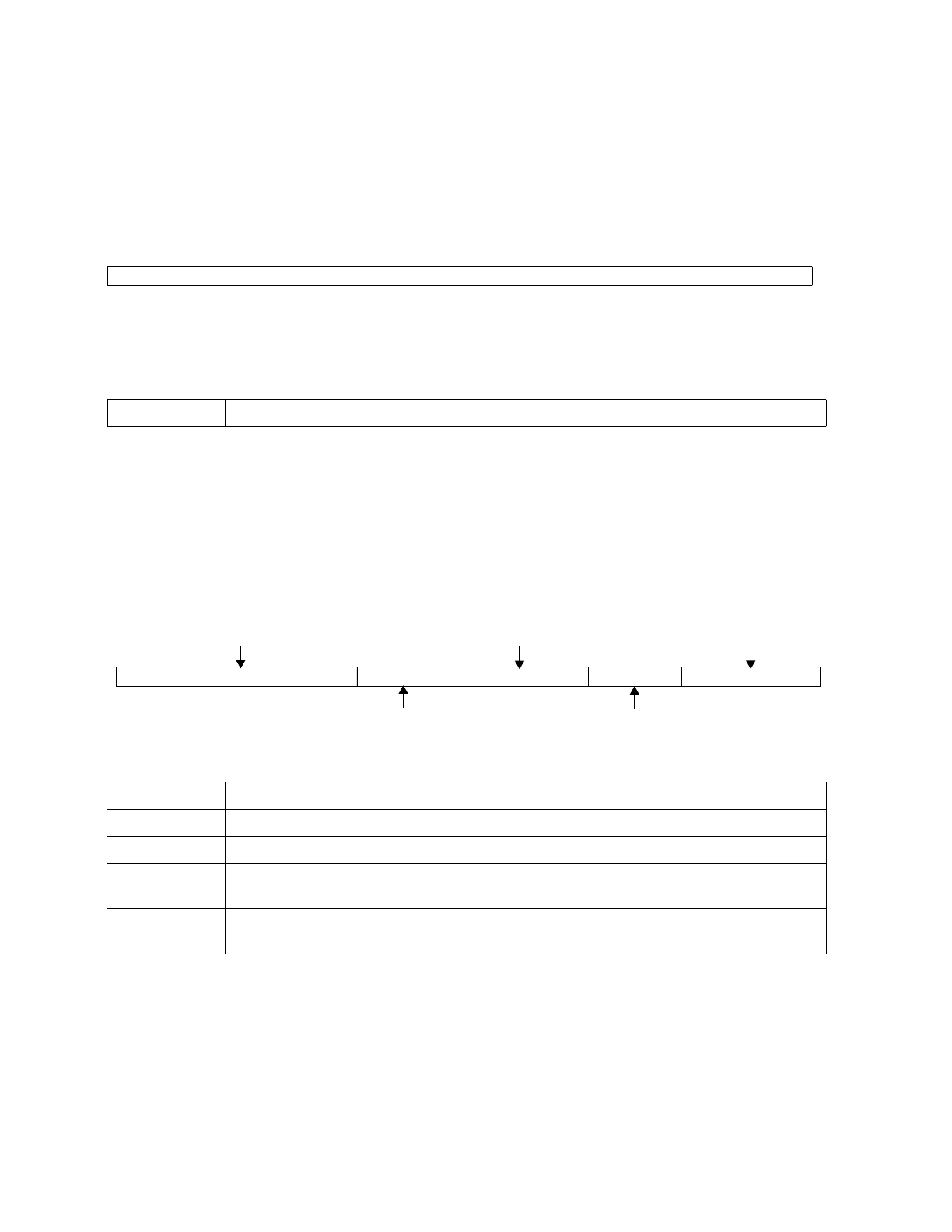

Figure 2-6. Special Purpose Register General (SPRG0–SPRG7)

0:31 General data Software value; no hardware usage.

Figure 2-7. Processor Version Register (PVR)

0:11 OWN Owner Identifier Identifies the owner of a core

12:15 PCF Processor Core Family Identifies the processor core family.

16:21 CAS Cache Array Sizes Identifies the cache array sizes.

22:25 PCL Processor Core Version Identifies the core version for a specific

combination of PVR[PCF] and PVR[CAS]

26:31 AID ASIC Identifier Assigned sequentially; identifies an ASIC

function, version, and technology

0 31

0 1112 1516 2122 2526 31

UDEF

OWN

CAS

PCL

AID