Programming Model 2-9

Table 2-2 and Table 2-3 list the PPC405 instructions that update the XER. In the tables, the syntax

“[o]” indicates that the instruction has an “o” form that updates XER[SO,OV], and a “non-o” form. The

syntax “[.]” indicates that the instruction has a “record” form that updates CR[CR0] (see “Condition

Register (CR)” on page 2-10), and a “non-record” form.

2.3.2.4 Special Purpose Register General (SPRG0–SPRG7)

USPRG0 and SPRG0–SPRG7 are provided for general purpose software use. For example, these

registers are used as temporary storage locations. For example, an interrupt handler might save the

contents of a GPR to an SPRG, and later restore the GPR from it. This is faster than a save/restore to

a memory location. These registers are written using mtspr and read using mfspr.

Access to USPRG0 is non-privileged for both read and write.

3:24 Reserved

25:31 TBC Transfer Byte Count Used by lswx and stswx; written by mtspr.

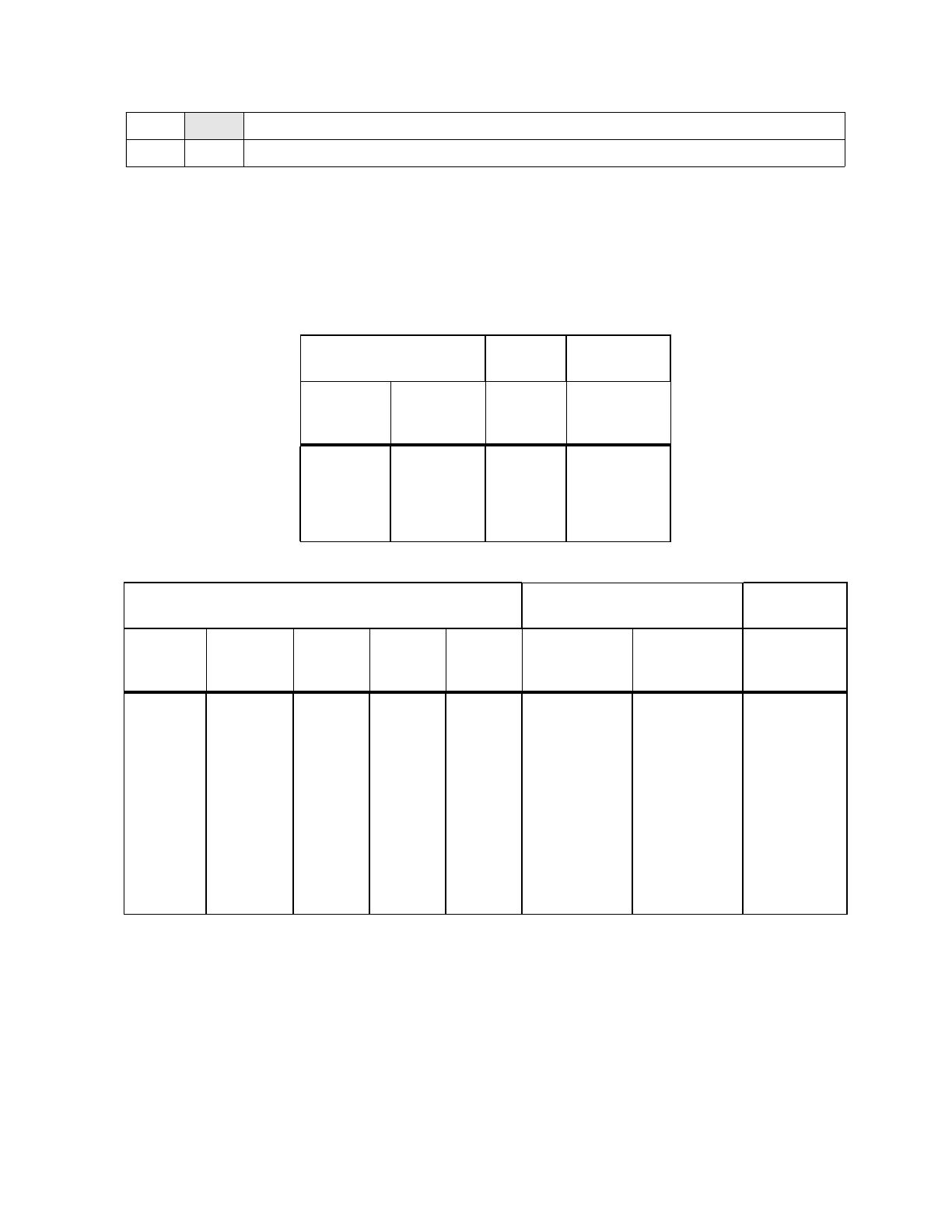

Table 2-2. XER[CA] Updating Instructions

Integer Arithmetic

Integer

Shift

Processor

Control

Add Subtract

Shift

Right

Algebraic

Register

Management

addc[o][.]

adde[o][.]

addic[.]

addme[o][.]

addze[o][.]

subfc[o][.]

subfe[o][.]

subfic

subfme[o][.]

subfze[o][.]

sraw[.]

srawi[.]

mtspr

mcrxr

Table 2-3. XER[SO,OV] Updating Instructions

Integer Arithmetic Auxiliary Processor

Processor

Control

Add Subtract Multiply Divide Negate

Multiply-

Accumulate

Negative

Multiply-

Accumulate

Register

Management

addo[.]

addco[.]

addeo[.]

addmeo[.]

addzeo[.]

subfo[.]

subfco[.]

subfeo[.]

subfmeo[.]

subfzeo[.]

mullwo[.] divwo[.]

divwuo[.]

nego[.] macchwo[.]

macchwso[.]

macchwsuo[.]

macchwuo[.]

machhwo[.]

machhwso[.]

machhwsuo[.]

machhwuo[.]

maclhwo[.]

maclhwso[.]

maclhwsuo[.]

maclhwuo[.]

nmacchwo[.]

nmacchwso[.]

nmachhwo[.]

nmachhwso[.]

nmaclhwo[.]

nmaclhwso[.]

mtspr

mcrxr