Fixed-Point Interrupts and Exceptions 5-25

5.19 Data TLB Miss Interrupt

The data TLB miss interrupt is generated if data translation is enabled and a valid TLB entry matching

the EA and PID is not present. The address of the instruction generating the untranslatable effective

data address is saved in SRR0. In addition, the hardware also saves the data address (that missed in

the TLB) in the DEAR.

The ESR is set to indicate whether the excepting operation was a store (includes dcbz, dcbi, dccci).

The interrupt is precise. Program flow vectors to EVPR[0:15] || 0x1100.

The following registers are modified to the values specified in Table 5-20

.

Programming Note: Data TLB miss interrupts can happen whenever data translation is enabled.

Therefore, ensure that SRR0 and SRR1 are saved before enabling translation in an interrupt

handler.

5.20 Instruction TLB Miss Interrupt

The instruction TLB miss interrupt is generated if instruction translation is enabled and execution is

attempted for an instruction for which a valid TLB entry matching the EA and PID for the instruction

fetch is not present. The instruction whose fetch caused the TLB miss is saved in SRR0.

The interrupt is precise with respect to the attempted execution of the instruction. Program flow

vectors to EVPR[0:15 || 0x1200.

The following are modified to the values specified in Table 5-21.

Programming Note: Instruction TLB miss interrupts can happen whenever instruction translation

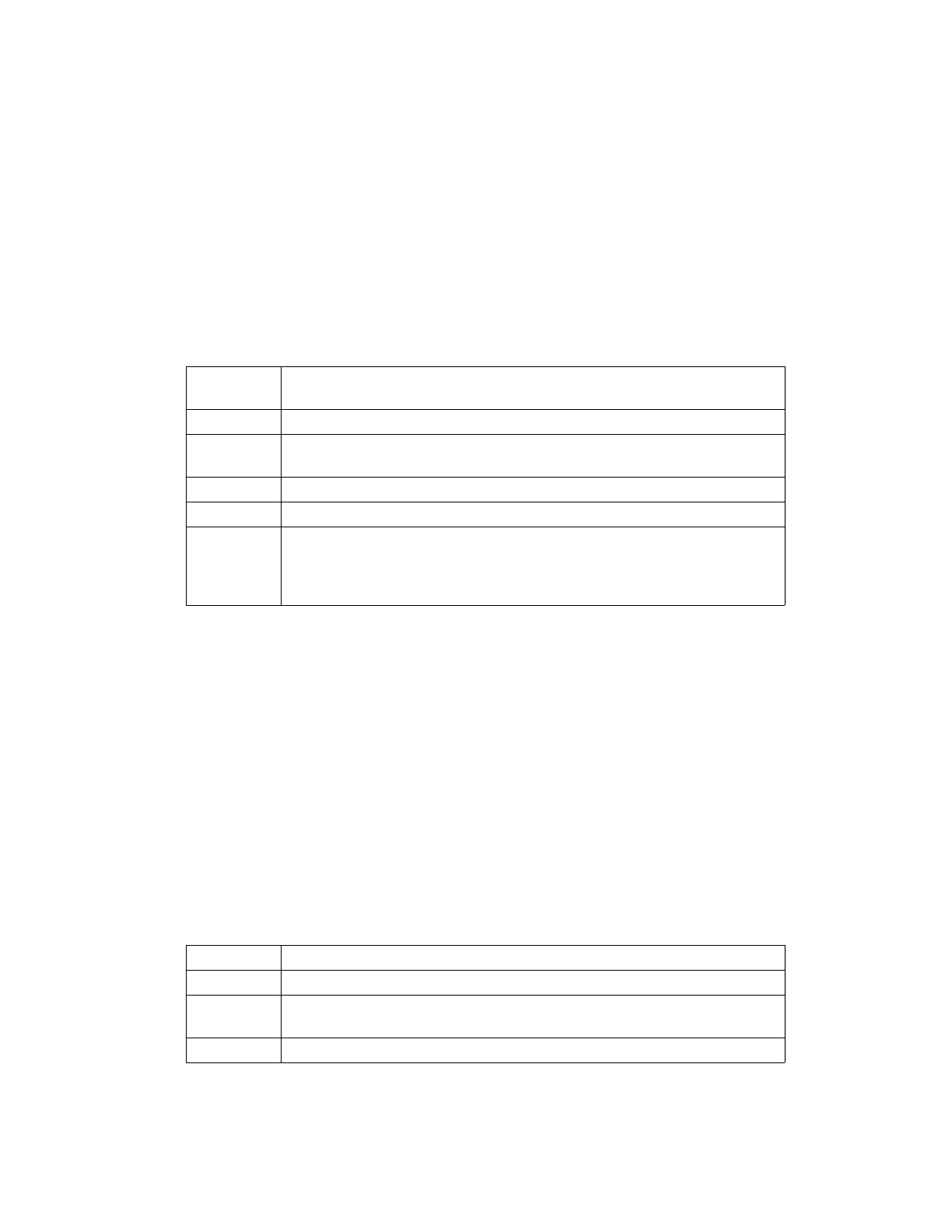

Table 5-20. Register Settings during Data TLB Miss Interrupts

SRR0 Set to the address of the instruction generating the effective address for

which no valid translation exists.

SRR1 Set to the value of the MSR at the time of the interrupt

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged

PC EVPR[0:15] || 0x1100

DEAR Set to the effective address of the failed access

ESR DST ← 1 if excepting operation is a store operation (includes dcbi, dcbz,

and dccci).

MCI ← unchanged

All other bits are cleared.

Table 5-21. Register Settings during Instruction TLB Miss Interrupts

SRR0 Set to the address of the instruction for which no valid translation exists.

SRR1 Set to the value of the MSR at the time of the interrupt

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged

PC EVPR[0:15] || 0x1200