10-2 PPC405 Core User’s Manual

10.5 Special Purpose Registers

Special Purpose Registers (SPRs), which are part of the PowerPC Embedded Environment, are

accessed using the mtspr and mfspr instructions. SPRs control the use of the debug facilities,

timers, interrupts, storage control attributes, and other architected processor resources.

Table 10-2 shows the mnemonics, names, and numbers of the SPRs. The columns under “SPRN” list

the register numbers used as operands in assembler language coding of the mfspr and mtspr

instructions. The column labeled “SPRF” lists the corresponding fields contained in the

machine code

of mfspr and mtspr. The SPRN field contains the five-bit subfields of the SPRF field, which are

reversed

in the machine code for the mfspr and mtspr instructions (SPRN ← SPRF

5:9

|| SPRF

0:4

)

for compatibility with the POWER Architecture. Note that the assembler handles the special coding

transparently.

All SPRs are privileged, except the Count Register (CTR), the Link Register (LR), SPR General

Purpose Registers (SPRG4–SPRG7, read-only), User SPR General Purpose Register (USPRG0),

and the Fixed-point Exception Register (XER). Note that access to the Time Base Lower (TBL) and

Time Base Upper (TBU) registers, when addressed as SPRs, is write-only and privileged. However,

when addressed as Time Base Registers (TBRs), read access to these registers is not privileged.

See “Time Base Registers” on page 4. for more information.

Table 10-2 lists the SPRs, their mnemonics and names, their numbers (SPRN) and the corresponding

SPRF numbers, and access. All SPR numbers not listed are reserved, and should be neither read nor

written.

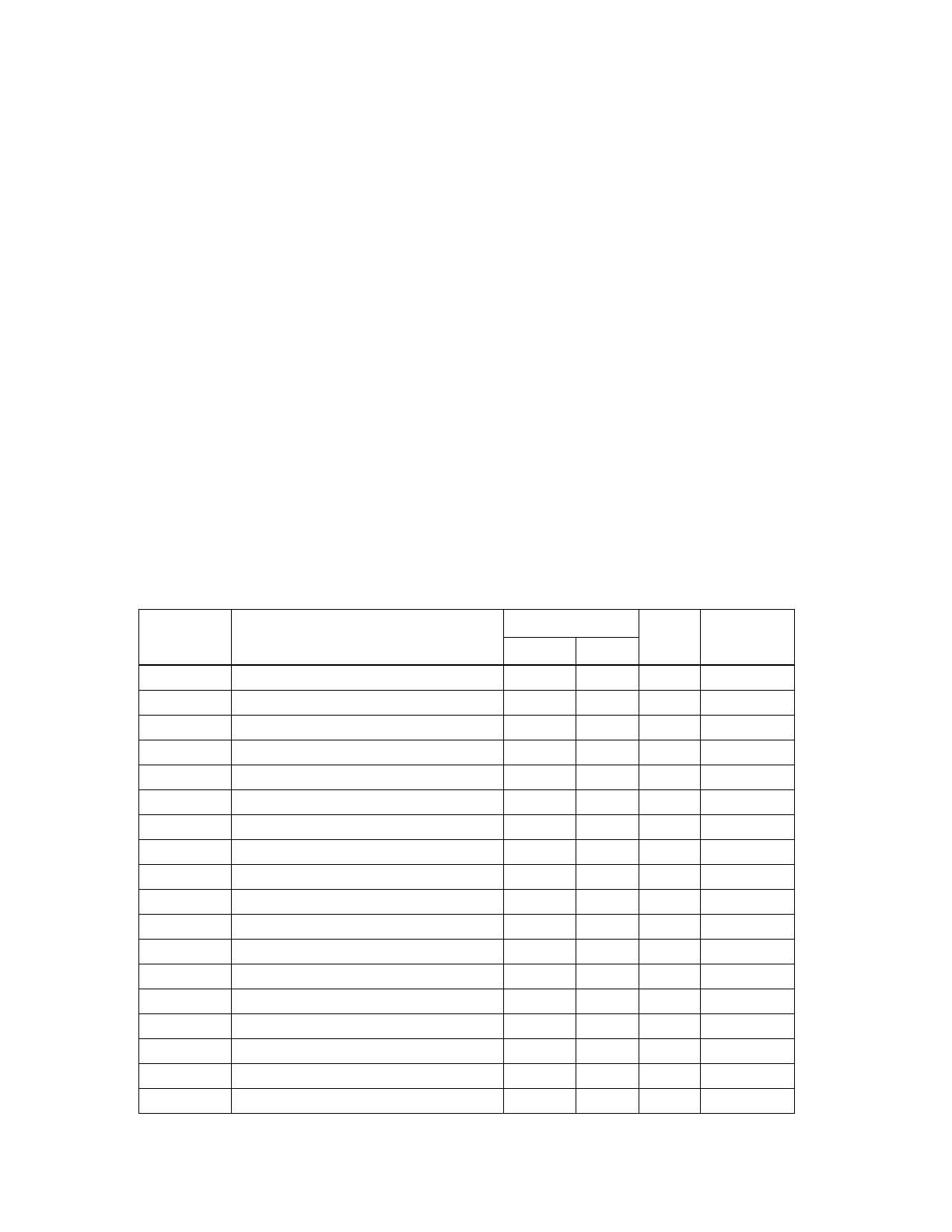

Table 10-2. Special Purpose Registers

Mnemonic Register Name

SPRN

SPRF AccessDecimal Hex

CCR0 Core Configuration Register 0 947 0x3B3 0x27D Read/Write

CTR Count Register 9 0x009 0x120 Read/Write

DAC1 Data Address Compare 1 1014 0x3F6 0x2DF Read/Write

DAC2 Data Address Compare 2 1015 0x3F7 0x2FF Read/Write

DBCR0 Debug Control Register 0 1010 0x3F2 0x25F Read/Write

DBCR1 Debug Control Register 1 957 0x3BD 0x3BD Read/Write

DBSR Debug Status Register 1008 0x3F0 0x21F Read/Clear

DCCR Data Cache Cachability Register 1018 0x3FA 0x35F Read/Write

DCWR Data Cache Write-through Register 954 0x3BA 0x35D Read/Write

DVC1 Data Value Compare 1 950 0x3B6 0x2DD Read/Write

DVC2 Data Value Compare 2 951 0x3B7 0x2FD Read/Write

DEAR Data Error Address Register 981 0x3D5 0x2BE Read/Write

ESR Exception Syndrome Register 980 0x3D4 0x29E Read/Write

EVPR Exception Vector Prefix Register 982 0x3D6 0x2DE Read/Write

IAC1 Instruction Address Compare 1 1012 0x3F4 0x29F Read/Write

IAC2 Instruction Address Compare 2 1013 0x3F5 0x2B5 Read/Write

IAC3 Instruction Address Compare 3 948 0x3B4 0x29D Read/Write

IAC4 Instruction Address Compare 4 949 0x3B5 0x2BD Read/Write