Programming Model 2-13

Adding the largest 32-bit twos-complement negative number, 0x8000 0000, to itself results in an

arithmetic overflow and 0x0000 0000 is recorded in the target register. CR[CR0]

EQ, SO

is set,

indicating a result of 0, but the infinitely precise result is negative.

The CR[CR0]

SO

subfield is a copy of XER[SO]. Instructions that do not alter the XER[SO] bit cannot

cause an overflow, but even for these instructions CR[CR0]

SO

is a copy of XER[SO].

Some instructions set CR[CR0] differently or do not specifically set any of the subfields. These

instructions include:

• Compare instructions

cmp, cmpi, cmpl, cmpli

• CR logical instructions

crand, crandc, creqv, crnand, crnor, cror, crorc, crxor, mcrf

• Move CR instructions

mtcrf, mcrxr

• stwcx.

The instruction descriptions provide detailed information about how the listed instructions alter

CR[CR0].

2.3.4 The Time Base

The PowerPC Architecture provides a 64-bit time base. “Time Base” on page 6-1 describes the

architected time base. Access to the time base is through two 32-bit time base registers (TBRs). The

least-significant 32 bits of the time base are read from the Time Base Lower (TBL) register and the

most-significant 32 bits are read from the Time Base Upper (TBU) register.

User-mode access to the time base is read-only, and there is no explicitly privileged read access to

the time base.

The mftb instruction reads from TBL and TBU. Writing the time base is accomplished by moving the

contents of a GPR to a pair of SPRs, which are also called TBL and TBU, using mtspr.

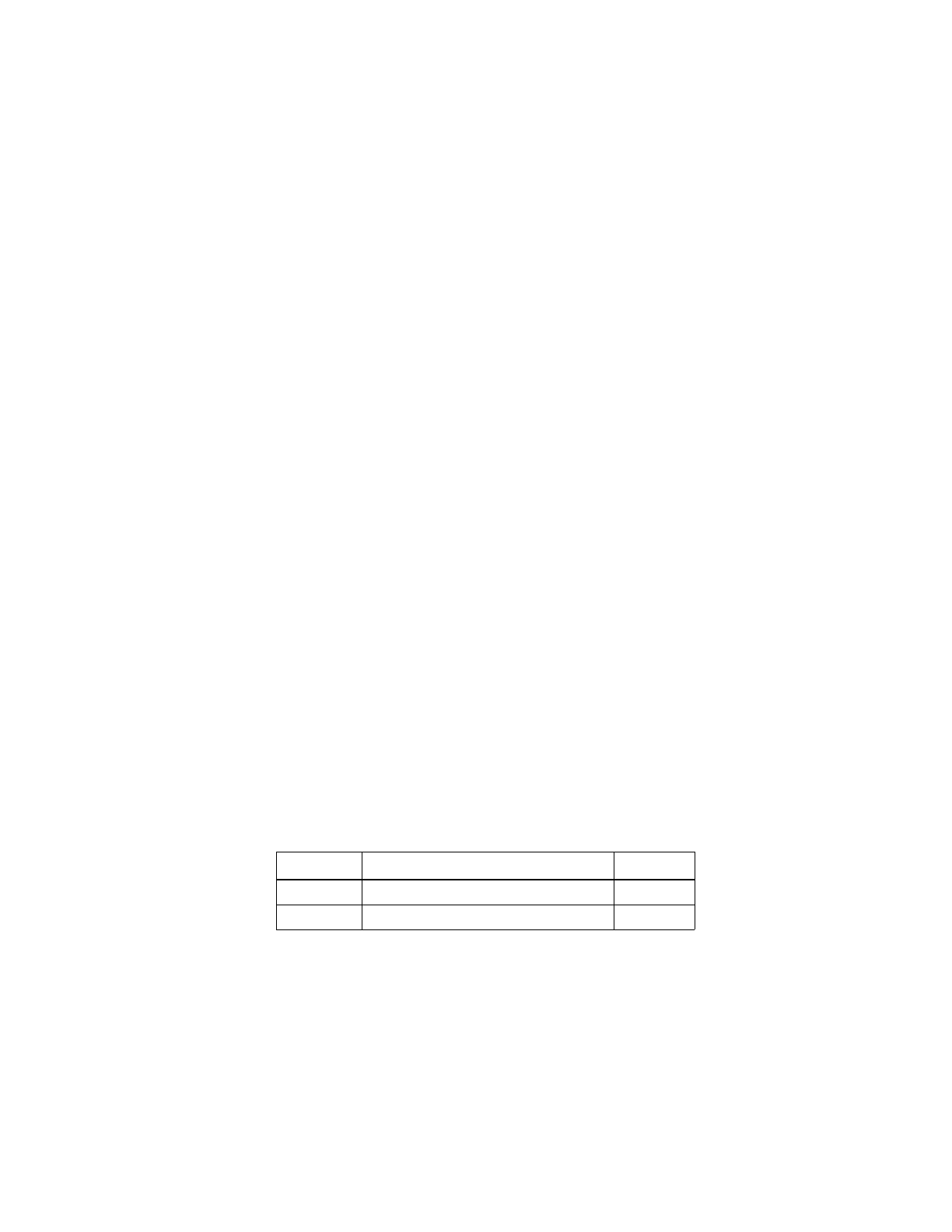

Table 2-4 shows the mnemonics and names of the TBRs.

2.3.5 Machine State Register (MSR)

The Machine State Register (MSR) controls processor core functions, such as the enabling or

disabling of interrupts and address translation.

The MSR is written from a GPR using the mtmsr instruction. The contents of the MSR can be read

into a GPR using the mfmsr instruction. MSR[EE] is set or cleared using the wrtee or wrteei

instructions.

Table 2-4. Time Base Registers

Mnemonic Register Name Access

TBL Time Base Lower (Read-only) Read-only

TBU Time Base Upper (Read-only) Read-only