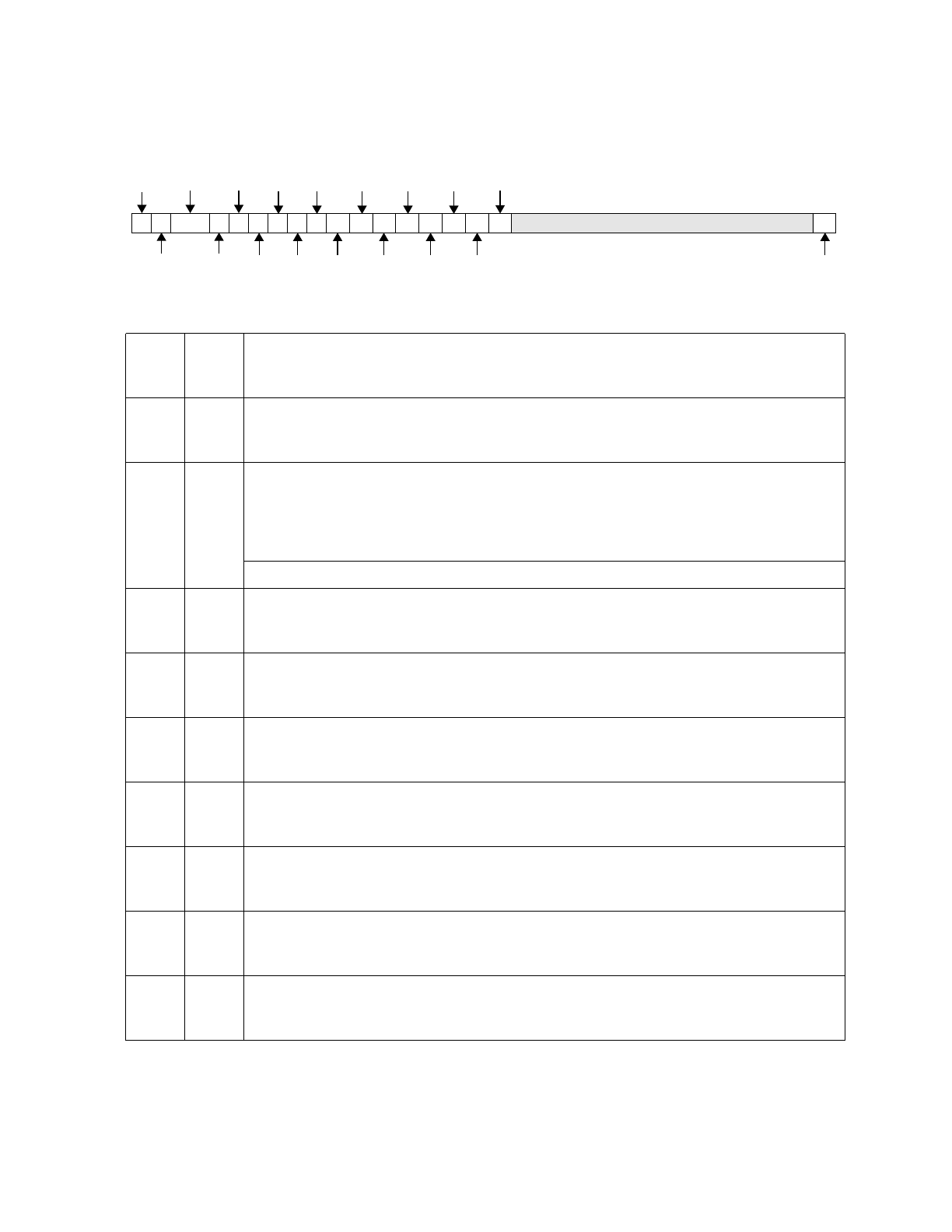

DBCR0

Debug Control Register 0

Register Summary 10-11

DBCR0

SPR 0x3F2

See “Debug Control Registers” on page 8-4.

Figure 10-5. Debug Control Register 0 (DBCR0)

0 EDM External Debug Mode

0 Disabled

1 Enabled

1 IDM Internal Debug Mode

0 Disabled

1 Enabled

2:3 RST Reset

00 No action

01 Core reset

10 Chip reset

11 System reset

Causes a processor reset request when

set by software.

Attention: Writing 01, 10, or 11 to this field causes a processor reset request.

4 IC Instruction Completion Debug Event

0 Disabled

1 Enabled

5 BT Branch Taken Debug Event

0 Disabled

1 Enabled

6 EDE Exception Debug Event

0 Disabled

1 Enabled

7 TDE Trap Debug Event

0 Disabled

1 Enabled

8 IA1 IAC 1 Debug Event

0 Disabled

1 Enabled

9 IA2 IAC 2 Debug Event

0 Disabled

1 Enabled

10 IA12 Instruction Address Range Compare 1–2

0 Disabled

1 Enabled

Registers IAC1 and IAC2 define an

address range used for IAC address

comparisons.

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 30 31

EDM

IDM

RST

IC

EDE

BT

IA1 IA34

TDE

FT

IA12

IA2

IA3

IA12X IA4

IA12T

IA34X

IA34T