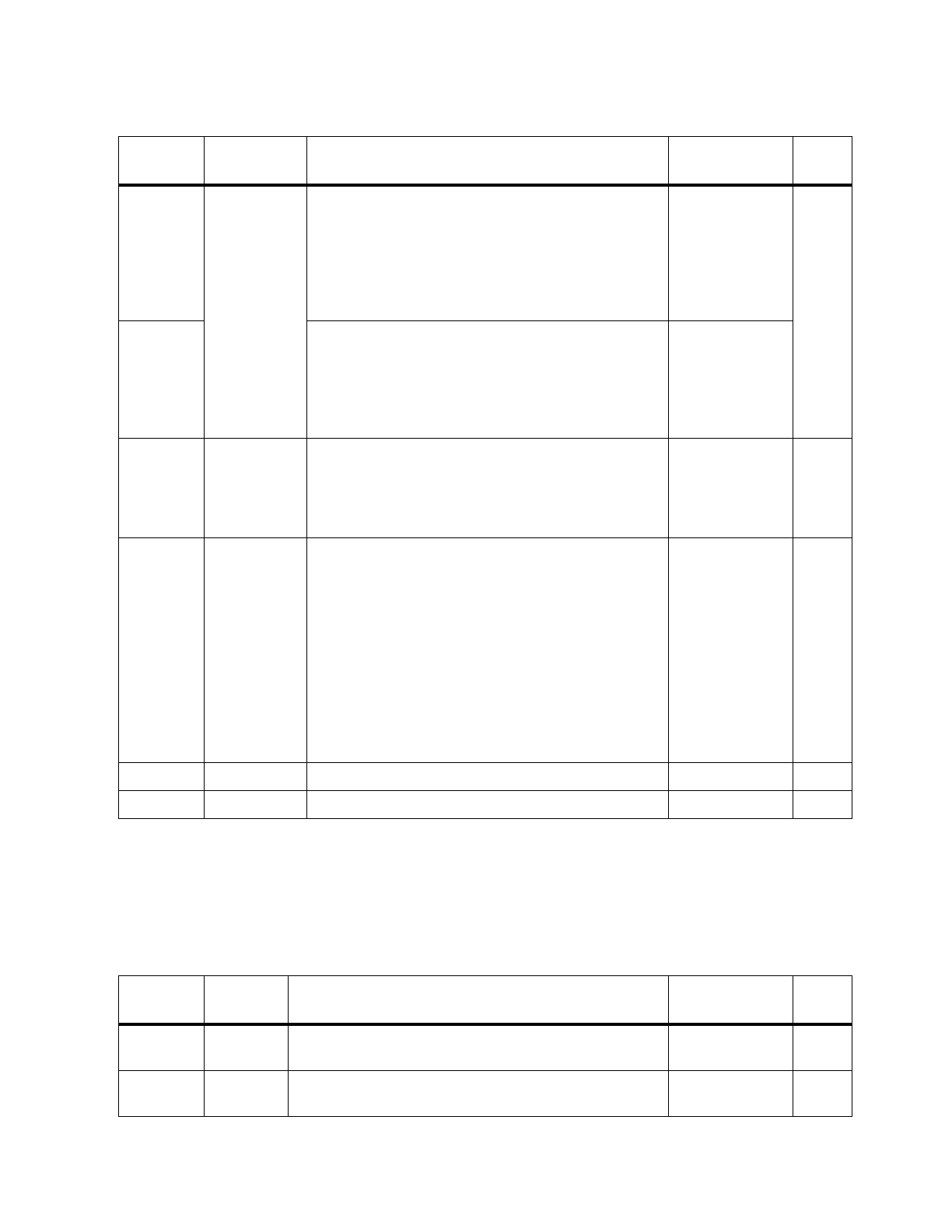

Instructions by Category B-7

B.3 Privileged Instructions

Table B-4 lists instructions that are under control of the MSR[PR] bit. These instructions are not

allowed to be executed when MSR[PR] = 1:

tlbsx RT,RA,RB Search the TLB array for a valid entry which

translates the EA

EA = (RA|0) + (RB).

If found,

(RT)

← Index of TLB entry.

If not found,

(RT) Undefined.

9-186

tlbsx. If found,

(RT)

← Index of TLB entry.

CR[CR0]

EQ

← 1.

If not found,

(RT) Undefined.

CR[CR0]

EQ

← 1.

CR[CR0]

LT,GT,SO

tlbsync tlbsync does not complete until all previous TLB-

update instructions executed by this processor have

been received and completed by all other processors.

For the PPC405 core, tlbsync is a no-op.

9-187

tlbwe RS, RA,WS If WS = 0:

Write TLBHI portion of the selected TLB entry from

RS.

Write the TID field of the selected TLB entry from the

PID register.

TLBHI[(RA)]

← (RS)

TLB[(RA)]

TID

← (PID)

24:31

If WS = 1:

Write TLBLO portion of the selected TLB entry from

RS.

TLBLO[(RA)]

← (RS)

9-188

wrtee RS Write value of RS

16

to MSR[EE]. 9-196

wrteei E Write value of E to MSR[EE]. 9-197

Table B-4. Privileged Instructions

Mnemonic Operands Function

Other Registers

Changed Page

dcbi RA, RB Invalidate the data cache block which contains the EA

(RA|0) + (RB).

9-50

dccci RA, RB Invalidate the data cache congruence class associated

with the EA (RA|0) + (RB).

9-56

Table B-3. Instructions in the IBM PowerPC Embedded Environment (continued)

Mnemonic Operands Function

Other Registers

Changed Page