Fixed-Point Interrupts and Exceptions 5-21

Attempted execution of an APU instruction while the APUc405exception signal is asserted) results in

a program interrupt. Similarly, attempted execution of an FPU instruction whilethe FPUc405exception

signal is asserted) also results in a program interrupt. The following also result in program interrupts:

attempted execution of an APU instruction while APUc405DcdAPUOp is asserted but

APUC405DcdValidOp is deasserted; and attempted execution of an FPU instruction while

APUc405DcdFpuOp but APUC405DcdValidOp is deasserted.

After any program interrupt, the contents of the MSR ar MSR[APA] = 0, an attempt to execute an

instruction intended for an APU causes a program interrupt if MSR[APE] = 0e written into SRR1 and

the MSR bits are written with the values shown in Table 5-13. The high-order 16 bits of the program

counter are written with the contents of the EVPR; the low-order 16 bits of the program counter are

written with 0x0700. Interrupt processing begins at the new address in the program counter.

Executing an rfi instruction restores the program counter from SRR0 and the MSR from SRR1, and

execution resumes at the address in the program counter.

5.13 FPU Unavailable Interrupt

If MSR[FP] = 0, an attempt to execute an FPU instruction for which an FPU asserts

APU_C405DcdFpuOp causes an FPU unavailable interrupt. The PPC405 FPU does not execute the

instruction, but writes the address of the FPU instruction into SRR0.

After an FPU unavailable interrupt occurs, the contents of the MSR are written into SRR1 and the

MSR bits are written with the values shown in Table 5-13. The high-order 16 bits of the program

counter are written with the contents of the EVPR; the low-order 16 bits of the program counter are

written with 0x0800. Interrupt processing begins at the new address in the program counter.

Executing an rfi instruction restores the program counter from SRR0 and the MSR from SRR1, and

execution resumes at the address in the program counter.

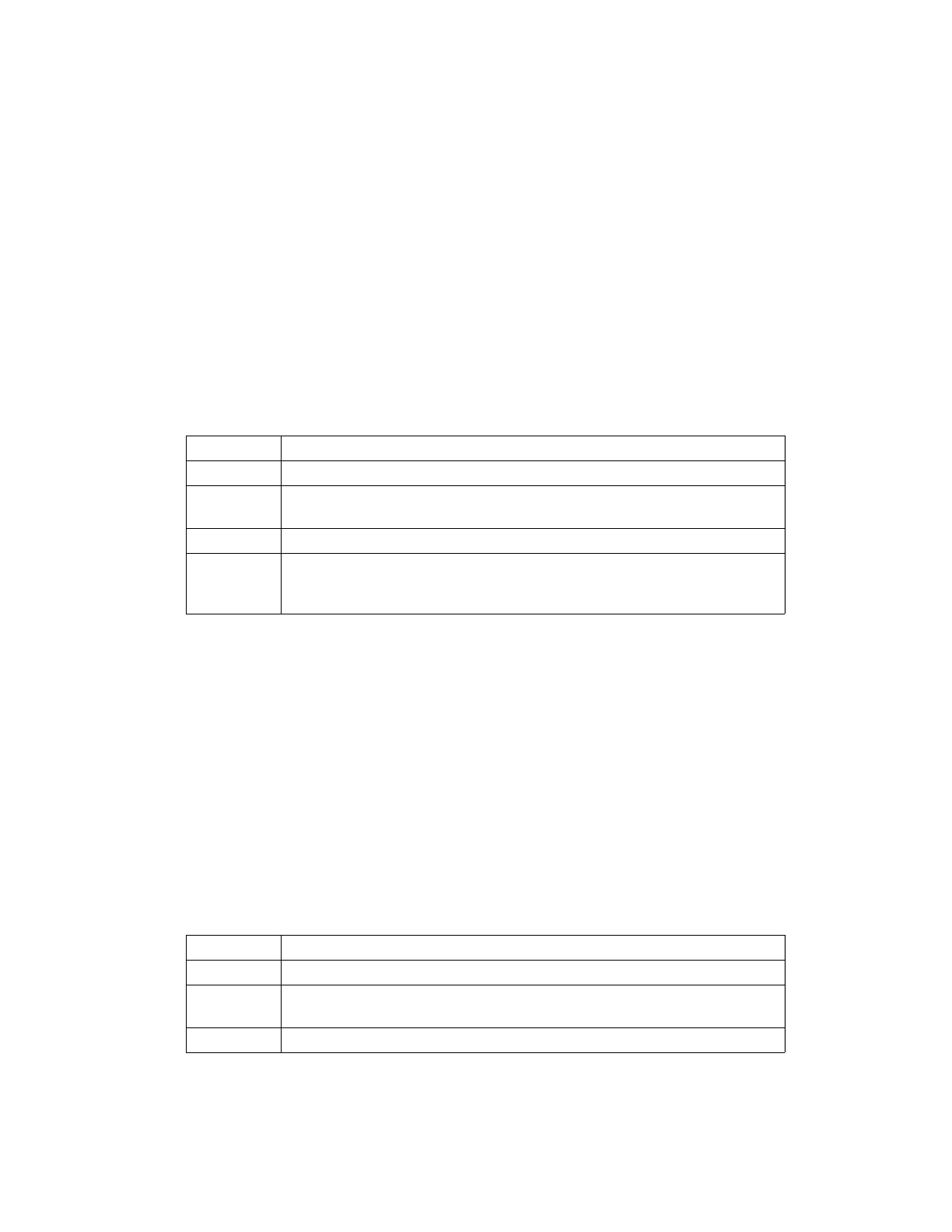

Table 5-13. Register Settings during Program Interrupts

SRR0 Written with the address of the excepting instruction

SRR1 Written with the contents of the MSR

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged

PC EVPR[0:15] || 0x0700

ESR Written with the type of program interrupt. (See Table 5-12)

MCI ← unchanged

All other bits are cleared.

Table 5-14. Register Settings during FPU Unavailable Interrupts

SRR0 Written with the address of the excepting instruction

SRR1 Written with the contents of the MSR

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged

PC EVPR[0:15] || 0x0800