Fixed-Point Interrupts and Exceptions 5-11

5.5.5 Exception Syndrome Register (ESR)

The ESR is a 32-bit register whose bits help to specify the exact cause of various synchronous

interrupts. These interrupts include instruction side machine checks, data storage interrupts, and

program interrupts, instruction storage interrupts, and data TLB miss interrupts.

“Instruction Machine Check Handling” on page 5-14 describes instruction machine checks. “Data

Storage Interrupt” on page 5-16 describes data storage interrupts. “Program Interrupt” on page 5-20

describes program interrupts.

Although interrupt handling routines are not required to reset the ESR, it is recommended that

instruction machine check handlers reset the ESR; “Instruction Machine Check Handling” on

page 5-14 describes why such resets are recommended.

The contents of the ESR can be written to a GPR using the mfspr instruction. The contents of a GPR

can be written to the ESR using the mtspr instruction.

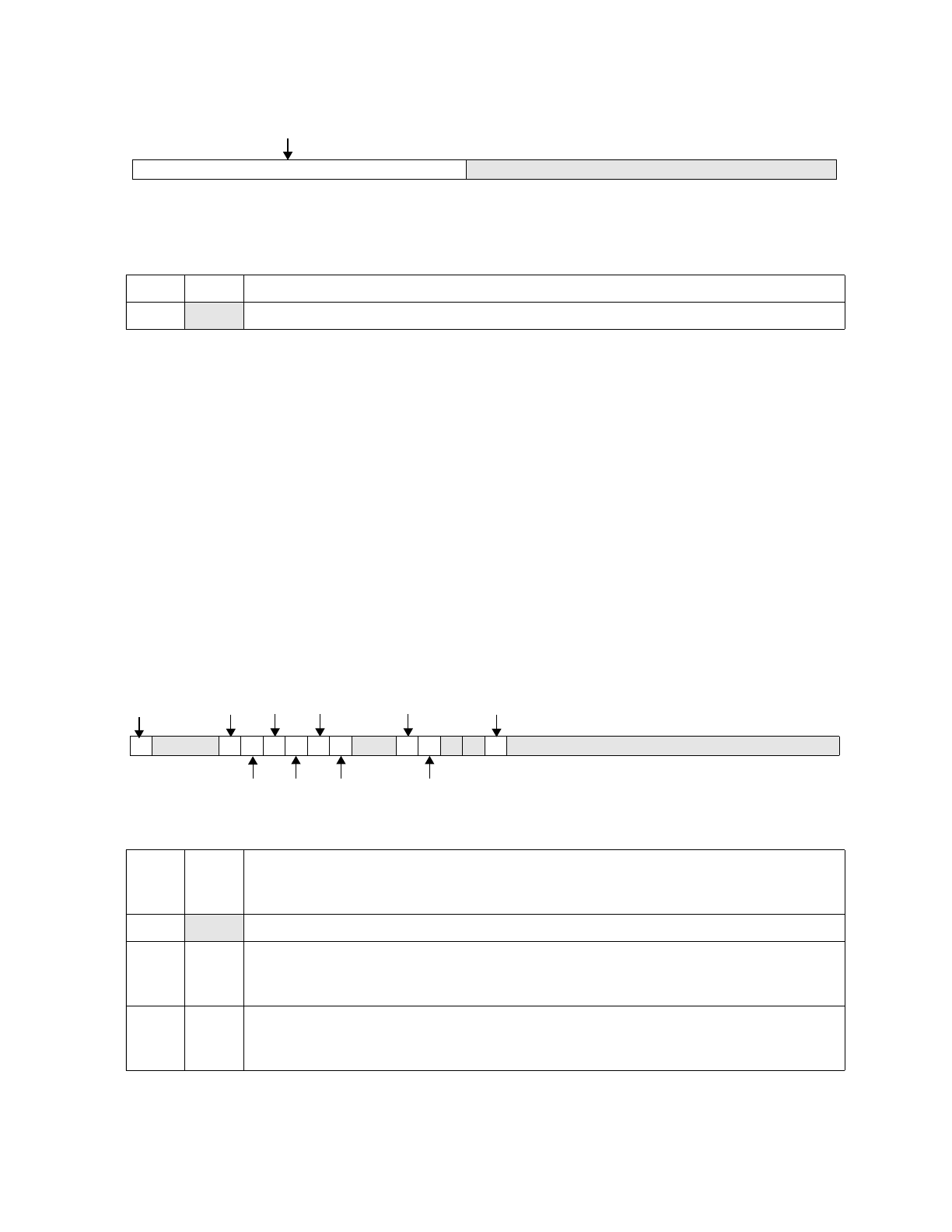

Figure 5-7 shows the ESR bit definitions.

Figure 5-6. Exception Vector Prefix Register (EVPR)

0:15 EVP Exception Vector Prefix

16:31

Reserved

Figure 5-7. Exception Syndrome Register (ESR)

0 MCI Machine check—instruction

0 Instruction machine check did not occur.

1 Instruction machine check occurred.

1:3

Reserved

4 PIL Program interrupt—illegal

0 Illegal Instruction error did not occur.

1 Illegal Instruction error occurred.

5 PPR Program interrupt—privileged

0 Privileged instruction error did not occur.

1 Privileged instruction error occurred.

01516 31

EVP

0 1 345678910 11 12 13 14 15 16 17 31

MCI PIL

PPR

PTR

PEU DIZ

PFP

PAP

U0FDST