B-44 PPC405 Core User’s Manual

B.14 Processor Management Instructions

The processor management instructions move data between GPRs and SPRs and DCRs in the

PPC405 core; these instructions also provide traps, system calls and synchronization controls.

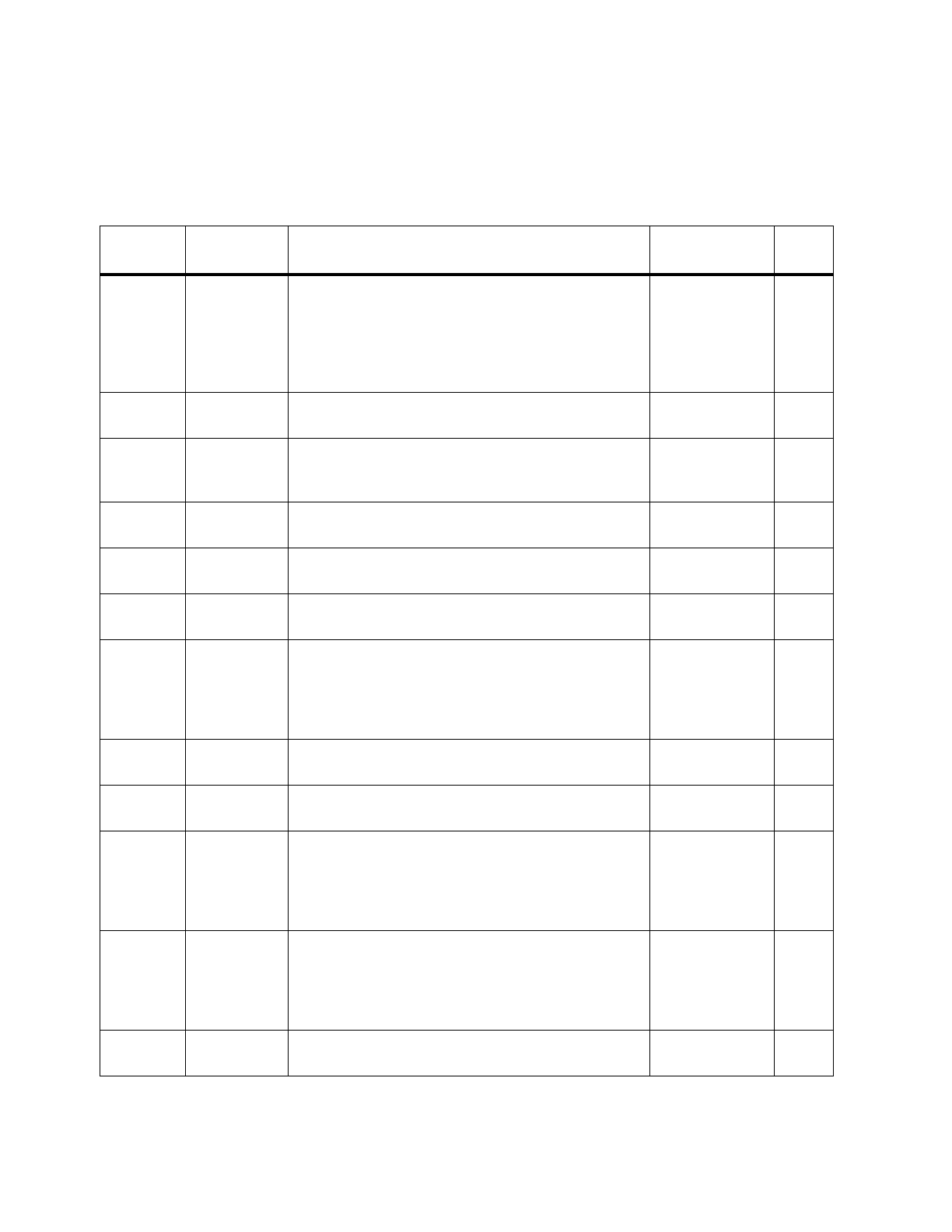

Table B-15. Processor Management Instructions

Mnemonic Operands Function

Other Registers

Changed Page

eieio Storage synchronization. All loads and stores that

precede the eieio instruction complete before any

loads and stores that follow the instruction access

main storage.

Implemented as sync, which is more restrictive.

9-61

isync Synchronize execution context by flushing the

prefetch queue.

9-70

mcrxr BF Move XER[0:3] into field CRn, where n

←BF.

CR[CRn]

← (XER[SO, OV, CA]).

(XER[SO, OV, CA])

←

3

0.

9-108

mfcr RT Move from CR to RT,

(RT)

← (CR).

9-108

mfdcr RT, DCRN Move from DCR to RT,

(RT)

← (DCR(DCRN)).

9-110

mfspr RT, SPRN Move from SPR to RT,

(RT)

← (SPR(SPRN)).

9-112

mtcrf FXM, RS Move some or all of the contents of RS into CR as

specified by FXM field,

mask

←

4

(FXM

0

) ||

4

(FXM

1

) || ... ||

4

(FXM

6

) ||

4

(FXM

7

).

(CR)

←((RS) ∧ mask) ∨ (CR) ∧¬mask).

9-116

mtdcr DCRN, RS Move to DCR from RS,

(DCR(DCRN))

← (RS).

9-117

mtspr SPRN, RS Move to SPR from RS,

(SPR(SPRN))

← (RS).

9-119

sc System call exception is generated.

(SRR1)

← (MSR)

(SRR0)

← (PC)

PC

← EVPR

0:15

|| 0x0C00

(MSR[WE, PR, EE, PE, DR, IR])

← 0

9-151

sync Synchronization. All instructions that precede sync

complete before any instructions that follow sync

begin.

When sync completes, all storage accesses initiated

before sync will have completed.

9-182

tw TO, RA, RB Trap exception is generated if, comparing (RA) with

(RB), any condition specified by TO is true.

9-190