Instruction Set 9-5

9.3.1 Operator Precedence

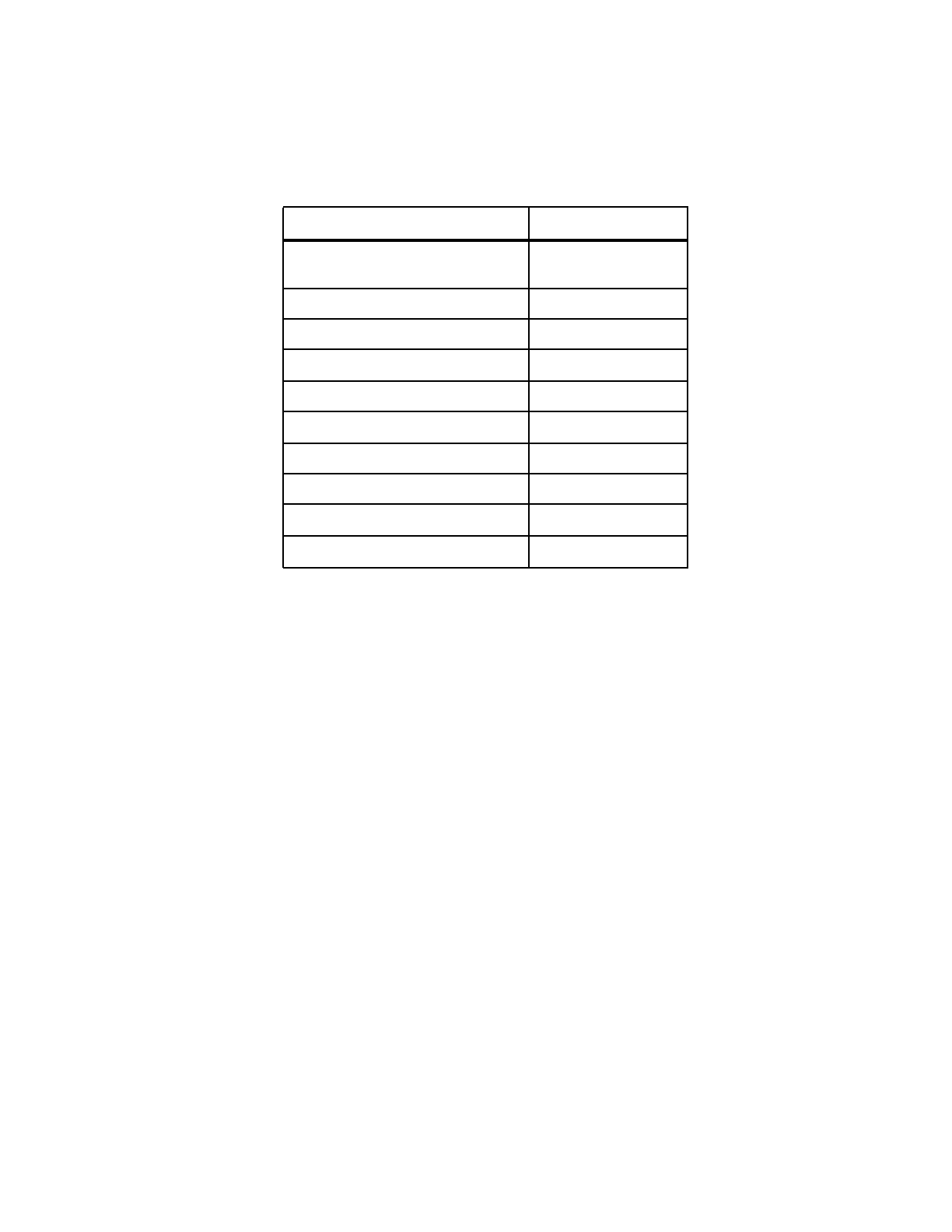

Table 9-2 lists the pseudocode operators and their associativity in descending order of precedence:

9.4 Register Usage

Each instruction description lists the registers altered by the instruction. Some register changes are

explicitly detailed in the instruction description (for example, the target register of a load instruction).

Other registers are changed, with the details of the change not included in the instruction description.

This category frequently includes the Condition Register (CR) and the Fixed-point Exception Register

(XER). For discussion of the CR, see “Condition Register (CR)” on page 2-10. For discussion of XER,

see “Fixed Point Exception Register (XER)” on page 2-7.

9.5 Alphabetical Instruction Listing

The following pages list the instructions available in the PPC405 core in alphabetical order.

Table 9-2. Operator Precedence

Operators Associativity

REG

b

, REG[FLD], function

evaluation

Left to right

n

b Right to left

¬, – (unary minus) Right to left

×, ÷

Left to right

+, – Left to right

||

Left to right

=,

≠, <, >, , Left to right

∧, ⊕ Left to right

∨

Left to right

←

None

<

u

>

u