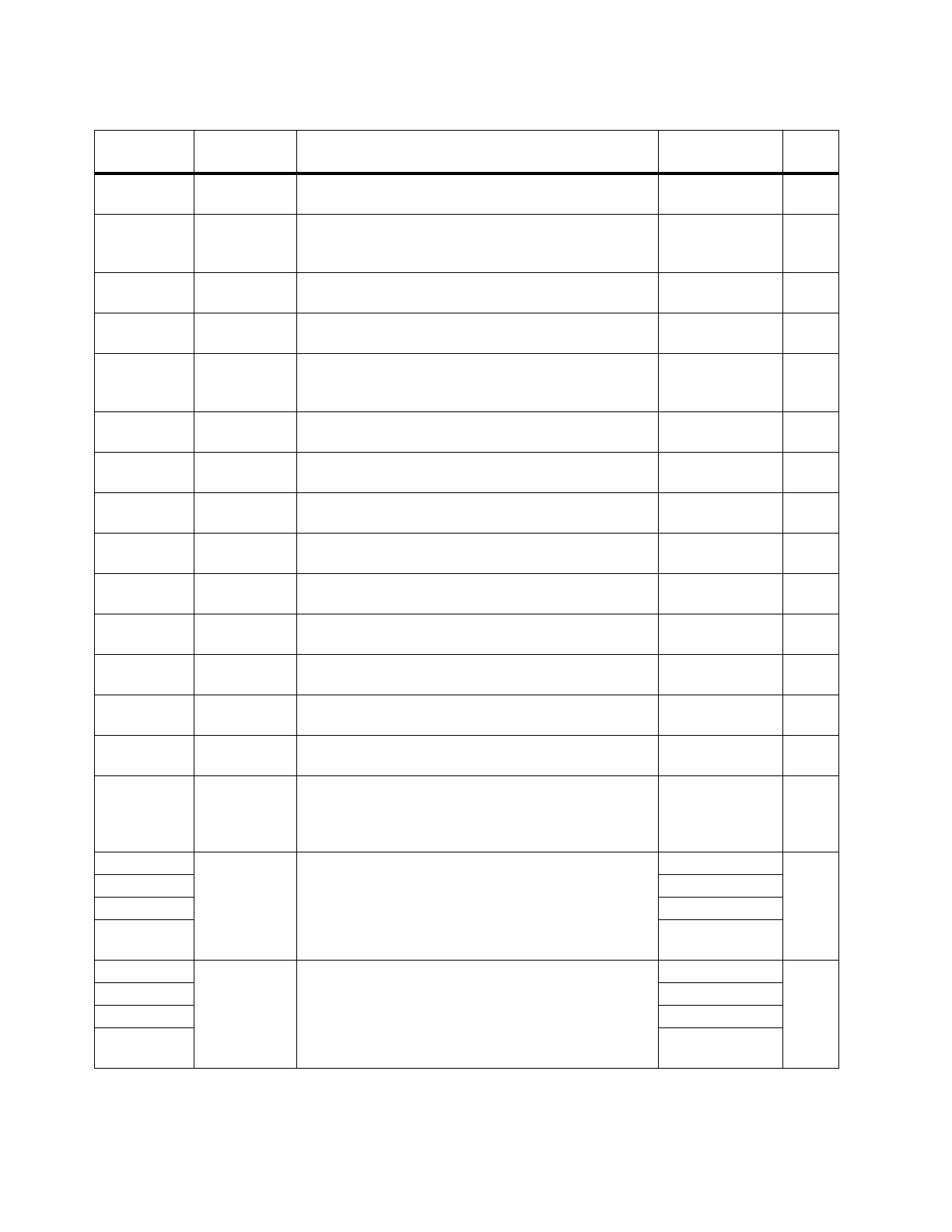

A-14 PPC405 Core User’s Manual

crnor BT, BA, BB NOR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

9-43

crnot bx, by Condition register not.

Extended mnemonic for

crnor bx,by,by

9-43

cror BT, BA, BB OR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

9-44

crorc BT, BA, BB OR bit (CR

BA

) with ¬(CR

BB

).

Place result in CR

BT

.

9-45

crset bx Condition register set.

Extended mnemonic for

creqv bx,bx,bx

9-41

crxor BT, BA, BB XOR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

9-46

dcba RA, RB Speculatively establish the data cache block which

contains the effective address (RA|0) + (RB).

9-47

dcbf RA, RB Flush (store, then invalidate) the data cache block

which contains the effective address (RA|0) + (RB).

9-49

dcbi RA, RB Invalidate the data cache block which contains the

effective address (RA|0) + (RB).

9-50

dcbst RA, RB Store the data cache block which contains the

effective address (RA|0) + (RB).

9-51

dcbt RA, RB Load the data cache block which contains the effective

address (RA|0) + (RB).

9-52

dcbtst RA,RB Load the data cache block which contains the effective

address (RA|0) + (RB).

9-53

dcbz RA, RB Zero the data cache block which contains the effective

address (RA|0) + (RB).

9-54

dccci RA, RB Invalidate the data cache congruence class

associated with the effective address (RA|0) + (RB).

9-56

dcread RT, RA, RB Read either tag or data information from the data

cache congruence class associated with the effective

address (RA|0) + (RB).

Place the results in RT.

9-57

divw RT, RA, RB Divide (RA) by (RB), signed.

Place result in RT.

9-59

divw. CR[CR0]

divwo XER[SO, OV]

divwo. CR[CR0]

XER[SO, OV]

divwu RT, RA, RB Divide (RA) by (RB), unsigned.

Place result in RT.

9-60

divwu. CR[CR0]

divwuo XER[SO, OV]

divwuo. CR[CR0]

XER[SO, OV]

Table A-1. PPC405 Instruction Syntax Summary (continued)

Mnemonic Operands Function

Other Registers

Changed Page