B-42 PPC405 Core User’s Manual

B.12 Interrupt Control Instructions

The interrupt control instructions allow the user to move data between general purpose registers and

the machine state register, return from interrupts and enable or disable maskable external interrupts.

Table B-13 shows the interrupt control instruction set.

B.13 TLB Management Instructions

The TLB management instructions read and write entries of the TLB array in the MMU, search the

TLB array for an entry which will translate a given address, invalidate all TLB entries, and synchronize

TLB updates with other processors.

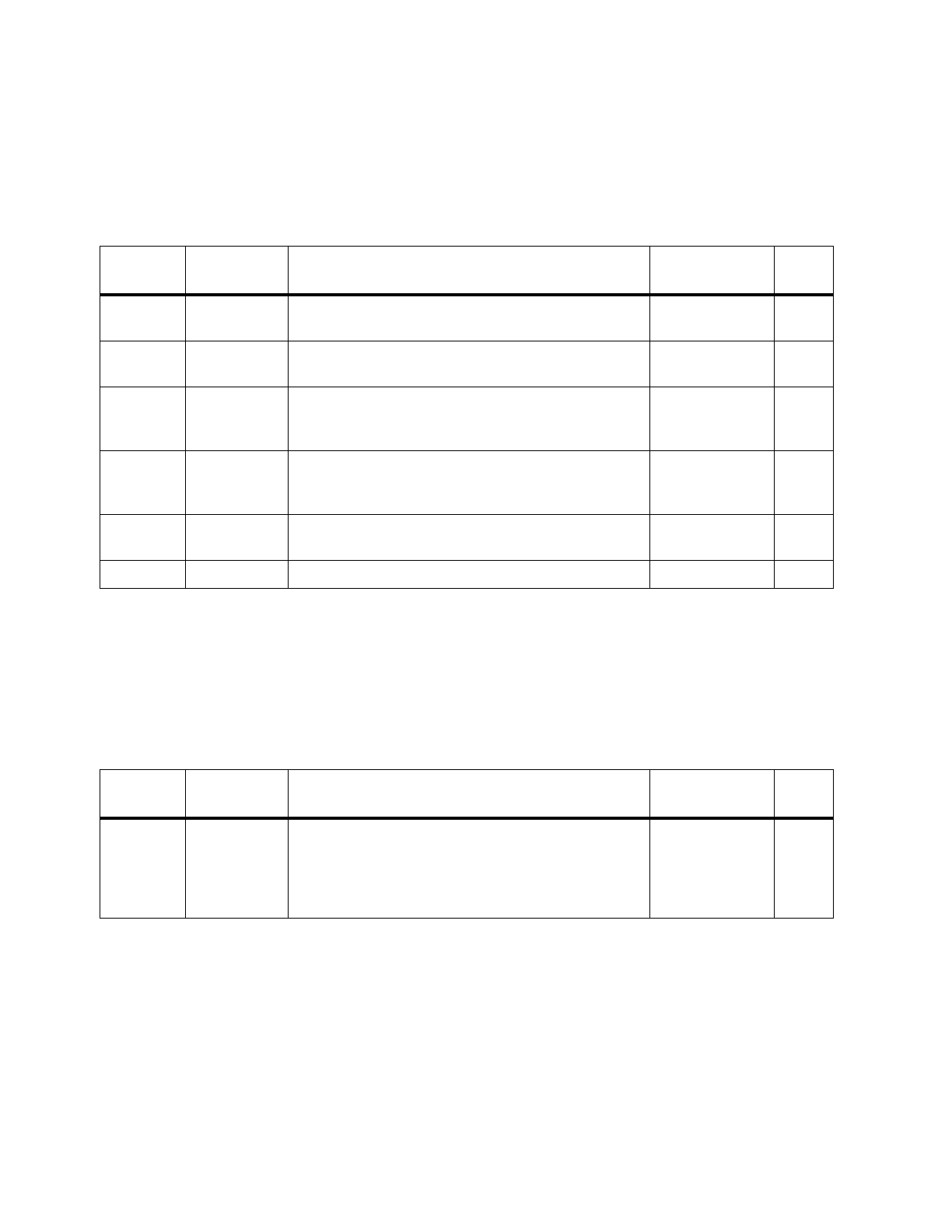

Table B-13. Interrupt Control Instructions

Mnemonic Operands Function

Other Registers

Changed Page

mfmsr RT Move from MSR to RT,

(RT)

← (MSR).

9-111

mtmsr RS Move to MSR from RS,

(MSR)

← (RS).

9-118

rfci Return from critical interrupt

(PC)

← (SRR2).

(MSR)

← (SRR3).

9-144

rfi Return from interrupt.

(PC)

← (SRR0).

(MSR)

← (SRR1).

9-144

wrtee RS Write value of RS

16

to the External Enable bit

(MSR[EE]).

9-196

wrteei E Write value of E to the External Enable bit (MSR[EE]). 9-197

Table B-14. TLB Management Instructions

Mnemonic Operands Function

Other Registers

Changed Page

tlbia All of the entries in the TLB are invalidated and

become unavailable for translation by clearing the

valid (V) bit in the TLBHI portion of each TLB entry.

The rest of the fields in the TLB entries are

unmodified.

9-183