Programming Model 2-15

2.3.6 Device Control Registers

Device Control Registers (DCRs), on-chip registers that exist architecturally outside the processor

core, are not part of the IBM PowerPC Embedded Environment. The Embedded Environment simply

defines the existence of a DCR address space and the instructions that access the DCRs, but does

not define any DCRs. The instructions that access the DCRs are mtdcr (move to device control

register) and mfdcr (move from device control register).

DCRs are used to control the operations of on-chip buses, peripherals, and some processor behavior.

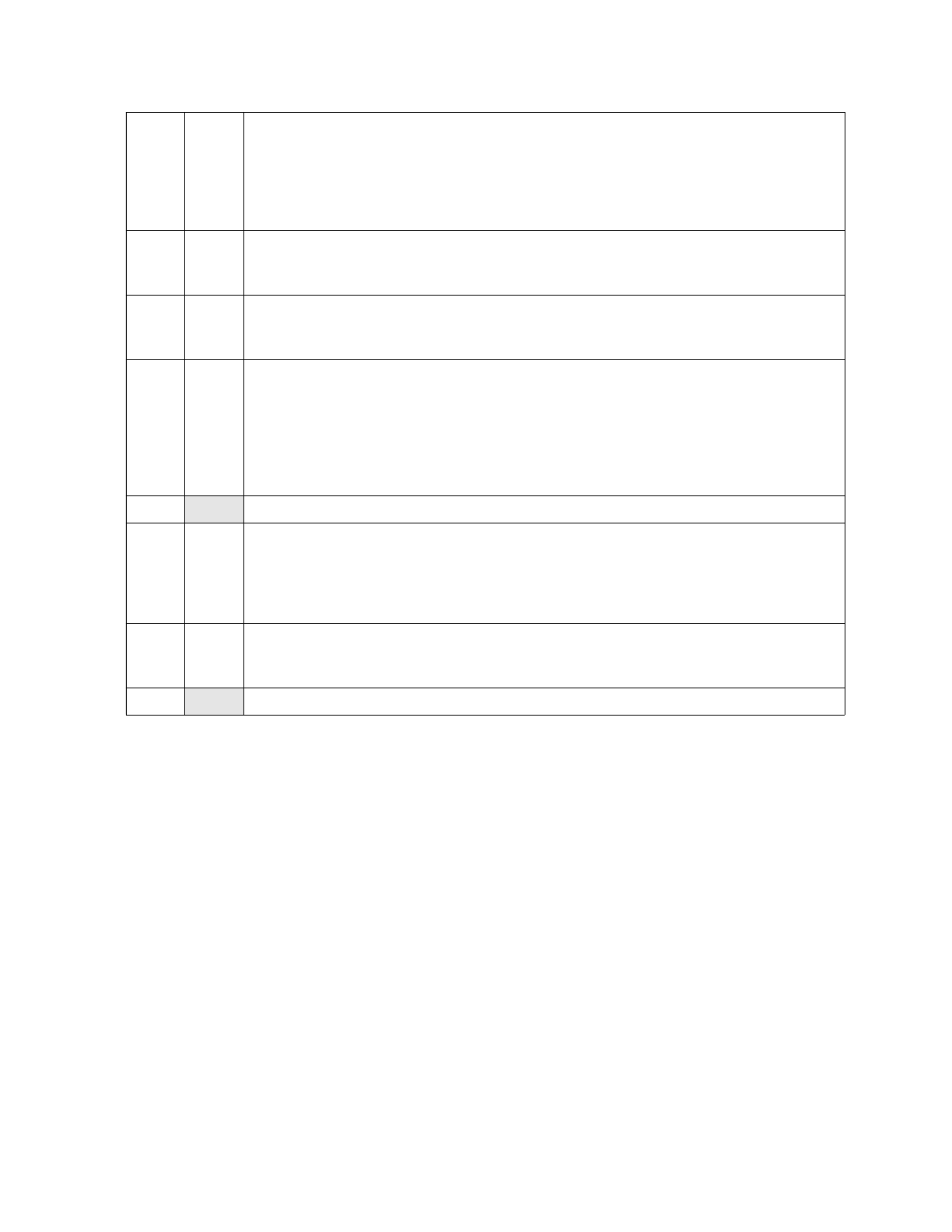

20 FE0 Floating-point exception mode 0

0 If MSR[FE1] = 0, ignore exceptions

mode; if MSR[FE1] = 1, imprecise

nonrecoverable mode

1 If MSR[FE1] = 0, imprecise recoverable

mode; if MSR[FE1] = 1, precise mode

21 DWE Debug Wait Enable

0 Debug wait mode is disabled.

1 Debug wait mode is enabled.

22 DE Debug Interrupts Enable

0 Debug interrupts are disabled.

1 Debug interrupts are enabled.

23 FE1 Floating-point exception mode 1

0 If MSR[FE0] = 0, ignore exceptions

mode; if MSR[FE0] = 1, imprecise

recoverable mode

1 If MSR[FE0] = 0, imprecise non-

recoverable mode; if MSR[FE0] = 1,

precise mode

24:25

Reserved

26 IR Instruction Relocate

0 Instruction address translation is

disabled.

1 Instruction address translation is

enabled.

27 DR Data Relocate

0 Data address translation is disabled.

1 Data address translation is enabled.

28:31

Reserved