2-24 PPC405 Core User’s Manual

Branch instructions are examined in DCD and PFB0 while all other instructions are decoded in DCD.

All instructions must pass through DCD before entering the EXU. The EXU contains the execute,

write-back and load write-back stages of the pipe. The results of most instructions are calculated

during the execute stage and written to the GPR file during the write back stage. Load instructions

write the GPR file during the load write-back stage.

2.7 Branch Processing

The PPC405, which provides a variety of conditional and unconditional branching instructions, uses

the branch prediction techniques described in “Branch Prediction” on page 3-35.

2.7.1 Unconditional Branch Target Addressing Options

The unconditional branches (b, ba, bl, bla) carry the displacement to the branch target address as a

signed 26-bit value (the 24-bit LI field right-extended with 0b00). The displacement enables

unconditional branches to cover an address range of ±32MB.

For the relative (AA = 0) forms (b, bl), the target address is the current instruction address (CIA, the

address of the branch instruction) plus the signed displacement.

For the absolute (AA = 1) forms (ba, bla), the target address is 0 plus the signed displacement. If the

sign bit (LI[0]) is 0, the displacement is the target address. If the sign bit is 1, the displacement is a

negative value and wraps to the highest memory addresses. For example, if the displacement is

0x3FF FFFC (the 26-bit representation of –4), the target address is 0xFFFF FFFC (0 – 4B, or 4 bytes

below the top of memory).

2.7.2 Conditional Branch Target Addressing Options

The conditional branches (bc, bca, bcl, bcla) carry the displacement to the branch target address as

a signed 16-bit value (the 14-bit BD field right-extended with 0b00). The displacement enables

conditional branches to cover an address range of ±32KB.

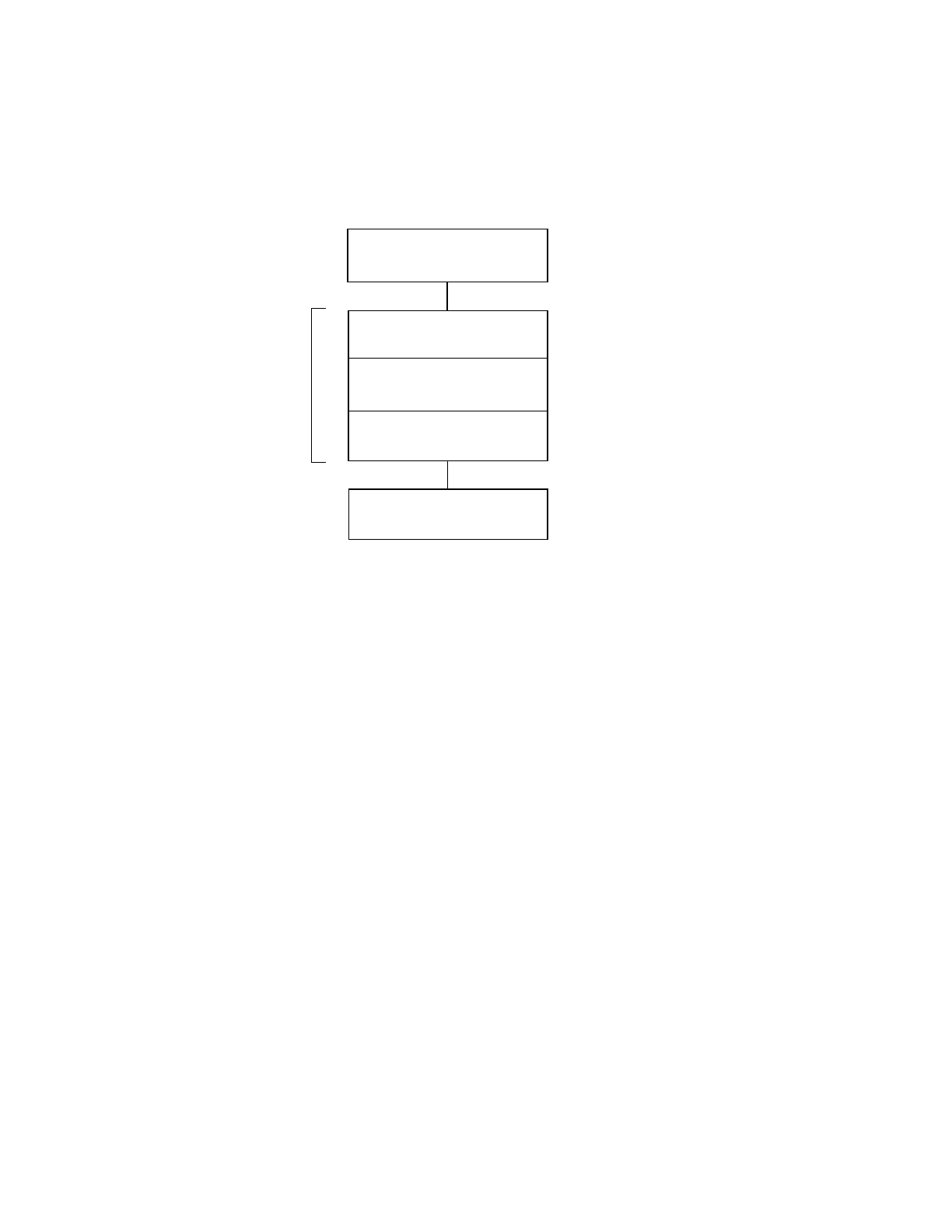

EXU

DCD

PFB0

PFB1

ICU

Figure 2-15. PPC405 Instruction Pipeline

Fetch

Dispatch

Queue

Instruction