Debugging 8-13

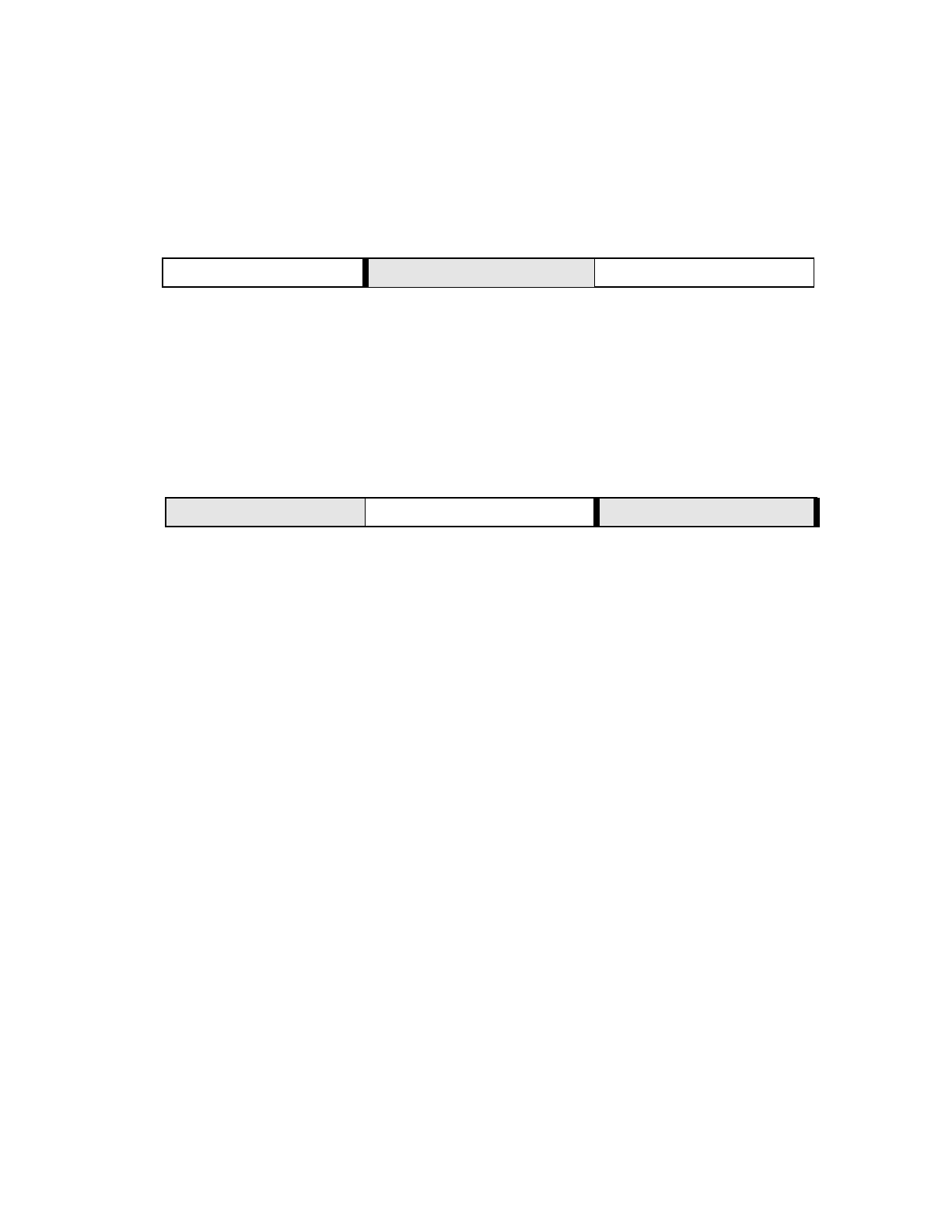

Figure 8-7 shows the range selected in an inclusive IAC range address compare. Note that the

address in IAC1 is considered part of the range, but the address in IAC2 is not, as shown in the

preceding examples. The thick lines indicate that the indicated address is included in the compare

results.

Figure 8-8 shows the range selected in an inclusive IAC range address compare. Note that the

address in IAC1 is not considered part of the range, but the address in IAC2 is, along with the highest

memory address, as shown in the preceding examples.

To toggle the range from inclusive to exclusive or from exclusive to inclusive on a IAC range debug

event, DBCR0[IA12T] (corresponding to range 1:2) and DBCR0[IA34T] (corresponding to range 3:4)

are used. If these fields are set, the DBCR0[IA12X] or DBCR0[IA34X] fields toggle on an IAC debug

event, changing the defined range.

When a toggle is enabled (DBCR0[IA12T] for range 1:2 or DBCR0[IA34T] = 1 for range 3:4), and

DBCR0[IDM] =1, DBCR0[EDM] = 0, and MSR[DE] = 0, IAC range comparisons for the corresponding

toggle field are disabled.

8.5.13 DAC Debug Event

This debug event occurs before execution of an instruction that accesses a data address that

matches the contents of the specified DAC register. DBCR1[D1R, D2R, D1W, D2W] enable DAC

debug events for address comparisons on DAC1 and DAC2 for read instructions, DAC2 for read

instructions, DAC1 for write instructions, DAC2 for write instructions respectively. Loads are reads and

stores are writes. DAC can be defined(DBCR1[D1R, D2R])as an exact address comparison to one of

the DACn registers or a range of addresses to compare defined by DAC1 and DAC2 registers.

8.5.13.1 DAC Exact Address Compare

In this mode, each DAC

n

register specifies an exact address to compare. Thes registers are enabled

by setting one or more of DBCR1[D1R,D2R,D1W,D2W] = 1, and disabling DAC range compare

DBCR1[DA12X] = 0. The corresponding DBSR[DR1,DR2,DW1,DW2] field displays the results of a

DAC debug event.

Figure 8-7. Inclusive IAC Range Address Compares

IAC1 IAC2

0

FFFF FFFF

Figure 8-8. Exclusive IAC Range Address Compares

IAC1 IAC2

0

FFFF FFFF