7-4 PPC405 Core User’s Manual

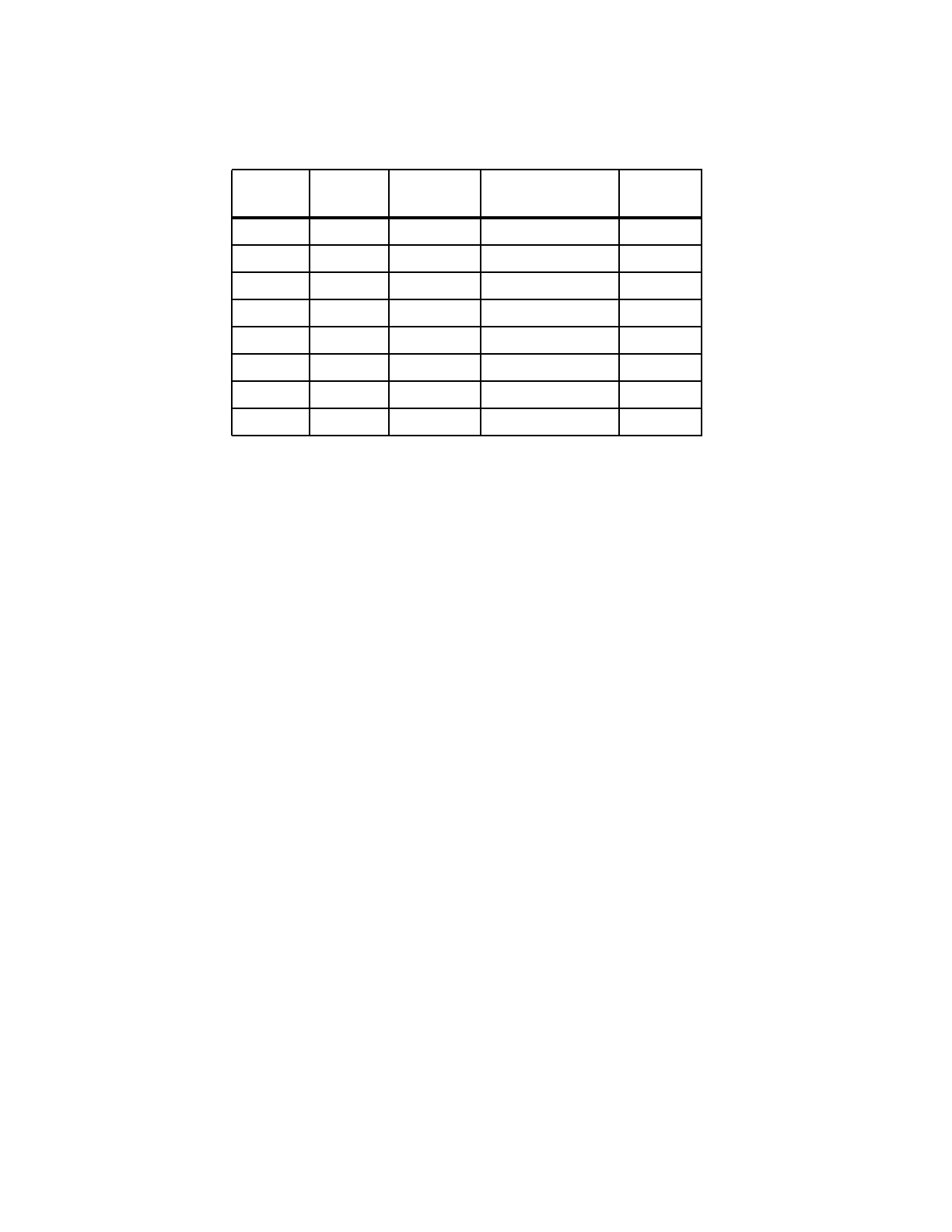

The exact comparison depends on the page size, as shown in Table 7-1.

SIZE (page size, 3 bits)

Selects one of the eight page sizes, 1KB–16MB, listed in Table 7-1.

V (valid,1 bit)

Indicates whether a TLB entry is valid and can be used for translation.

A valid TLB entry implies read access, unless overridden by zone protection. TLB_entry[V] can be

written using a tlbwe instruction. The tlbia instruction invalidates all TLB entries.

TID (translation ID, 8 bits)

Loaded from the PID register during a tlbwe operation. The TID value is compared with the PID value

during a TLB access. The TID provides a convenient way to associate a translation with one of 255

unique software entities, typically a process or thread ID maintained by operating system software.

Setting TLBHI_entry[TID] = 0x00 disables TID-PID comparison and identifies a TLB entry as valid for

all processes; the value of the PID register is then irrelevant.

7.3.2.2 Translation Field

When a TLB entry is identified as matching an EA (and possibly the PID), TLBLO_entry[RPN] defines

how the EA is translated.

RPN (real page number, 22 bits)

Replaces some, or all, of EA

0:21

, depending on page size. For example, a 16KB page uses EA

0:17

for

comparison. The translation mechanism replaces EA

0:17

with TLBLO_entry[RPN]

0:17

to form the

physical address, and EA

18:31

becomes the real page offset, as illustrated in Figure 7-1.

Programming Note: Software must set all unused bits of RPN (as determined by page size) to 0.

See Table 7-1.

Table 7-1. TLB Fields Related to Page Size

Page

Size

SIZE

Field

n

Bits

Compared

EPN to EA

Comparison

RPN Bits

Set to 0

1KB 000 22 EPN

0:21

↔ EA

0:21

—

4KB 001 20 EPN

0:19

↔ EA

0:19

RPN

20:21

16KB 010 18 EPN

0:17

↔ EA

0:17

RPN

18:21

64KB 011 16 EPN

0:15

↔ EA

0:15

RPN

16:21

256KB 100 14 EPN

0:13

↔ EA

0:13

RPN

14:21

1MB 101 12 EPN

0:11

↔ EA

0:11

RPN

12:21

4MB 110 10 EPN

0:9

↔ EA

0:9

RPN

10:21

16MB 111 8 EPN

0:7

↔ EA

0:7

RPN

8:21