Timer Facilities 6-9

6.5 Timer Control Register (TCR)

The TCR controls PIT, FIT, and watchdog timer operation.

The TCR[WRC] field is cleared to 0 by all processor resets. (Chapter 3, “Initialization,” describes the

types of processor reset.) This field is set only by software. However, hardware does not allow

software to clear the field after it is set. After software writesa1toabitinthefield, that bit remains a

1 until any reset occurs. This prevents errant code from disabling the watchdog timer reset function.

All processor resets clear TCR[ARE] to 0, disabling the auto-reload feature of the PIT.

5 FIS FIT Interrupt Status

0 No FIT interrupt is pending.

1 FIT interrupt is pending.

6:31

Reserved

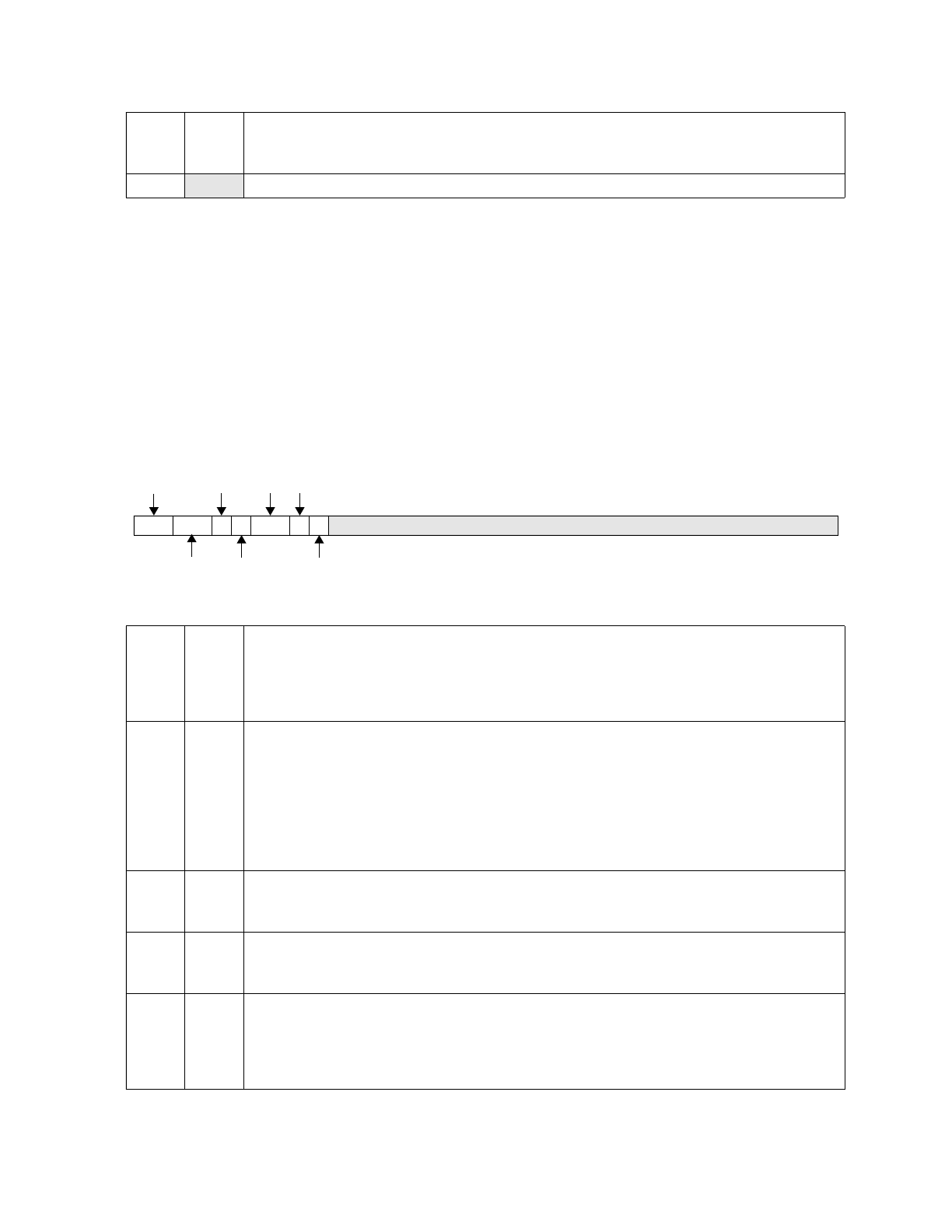

Figure 6-7. Timer Control Register (TCR)

0:1 WP Watchdog Period

00 2

17

clocks

01 2

21

clocks

10 2

25

clocks

11 2

29

clocks

2:3 WRC Watchdog Reset Control

00 No Watchdog reset will occur.

01 Core reset will be forced by the

Watchdog.

10 Chip reset will be forced by the

Watchdog.

11 System reset will be forced by the

Watchdog.

TCR[WRC] resets to 00.

This field can be set by software, but

cannot be cleared by software, except by a

software-induced reset.

4 WIE Watchdog Interrupt Enable

0 Disable watchdog interrupt.

1 Enable watchdog interrupt.

5 PIE PIT Interrupt Enable

0 Disable PIT interrupt.

1 Enable PIT interrupt.

6:7 FP FIT Period

00 2

9

clocks

01 2

13

clocks

10 2

17

clocks

11 2

21

clocks

012345678910 31

WP

WRC

WIE

PIE

FP FIE

ARE