Debugging 8-19

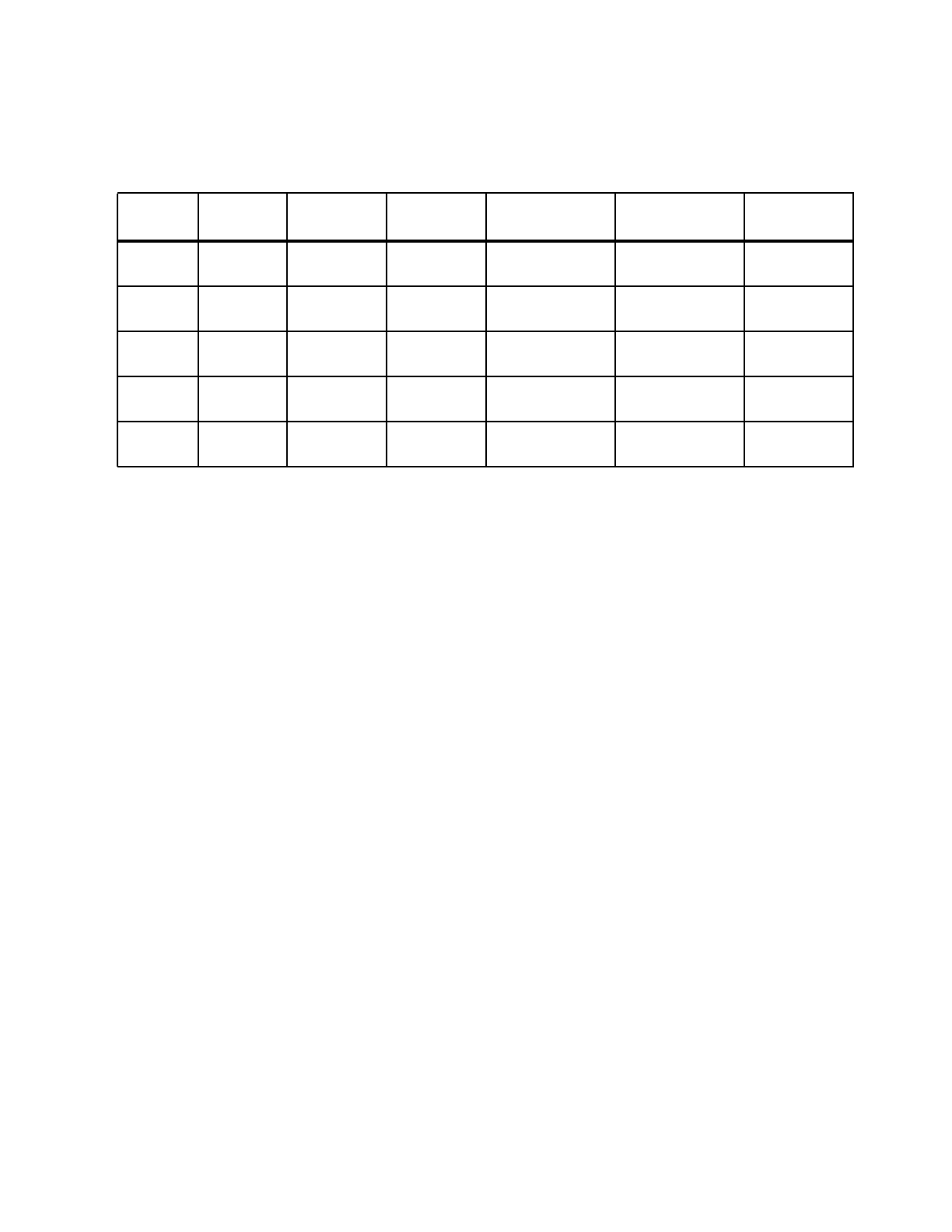

Table 8-6 illustrates comparisons for misaligned DVC accesses. In the “DVC1” and “DVC2” columns,

“x” indicates a don’t care.

Note: Misaligned accesses stop the processor on the instruction causing the compare hit. The

second part of an instruction is not performed if the first part of the compare hits.

8.5.15 Imprecise Debug Event

The imprecise debug event is not an independent debug event, but indicates that a debug event

occurred while MSR[DE] = 0. This is useful in internal debug mode if a debug event occurs while in a

critical interrupt handler. On return from interrupt, a debug interrupt occurs if MSR[DE] = 1. If

DBSR[IDE] = 1, the debug event causing the interrupt occurred sometime earlier, not immediately

after a debug event.

8.6 Debug Interface

The PPC405 core provides a and trace interfaces to support hardware and software test and debug.

Typically, the JTAG interface connects to a debug port external to the PPC405; the debug port is

typically connected to a JTAG connector on a processor board.

The trace interface connects to a trace port, also external to the PPC405, that is typically connected

to a trace connector on the processor board.

8.6.1 IEEE 1149.1 Test Access Port (JTAG Debug Port)

The IEEE 1149.1 Test Access Port (TAP), commonly called the JTAG (Joint Test Action Group) debug

port, is an architectural standard described in IEEE Std 1149.1–1990,

IEEE Standard Test Access

Port and Boundary Scan Architecture

. The standard describes a method for accessing internal chip

facilities using a four- or five-signal interface.

The JTAG debug port, originally designed to support scan-based board testing, is enhanced to

support the attachment of debug tools. The enhancements, which comply with the IEEE 1149.1

Table 8-6. Comparisons for Misaligned DVC Accesses

Access Operation DVC1 (Hex) DVC2 (Hex)

DBCR1[DV1BE]

Setting

DBCR1[DV2BE]

Setting

DBCR1[D2S]

Setting

Word

(Offset 1)

AND xx112233 44xxxxxx 123 0

01

Word

(Offset 2)

AND xxxx1122 3344xxxx 23 01

10

Word

(Offset 3)

AND xxxxxx11 223344xx 3 012

10

Halfword

(Offset 1)

AND xx1122xx 12 12

10

Halfword

(Offset 3)

AND xxxxxx11 22xxxxxx 3 0

10