3-2 PPC405 Core User’s Manual

Two SPRs contain status on the type of reset that has occurred. The Debug Status Register (DBSR)

contains the most recent reset type. The Timer Status Register (TSR) contains the most recent

watchdog reset.

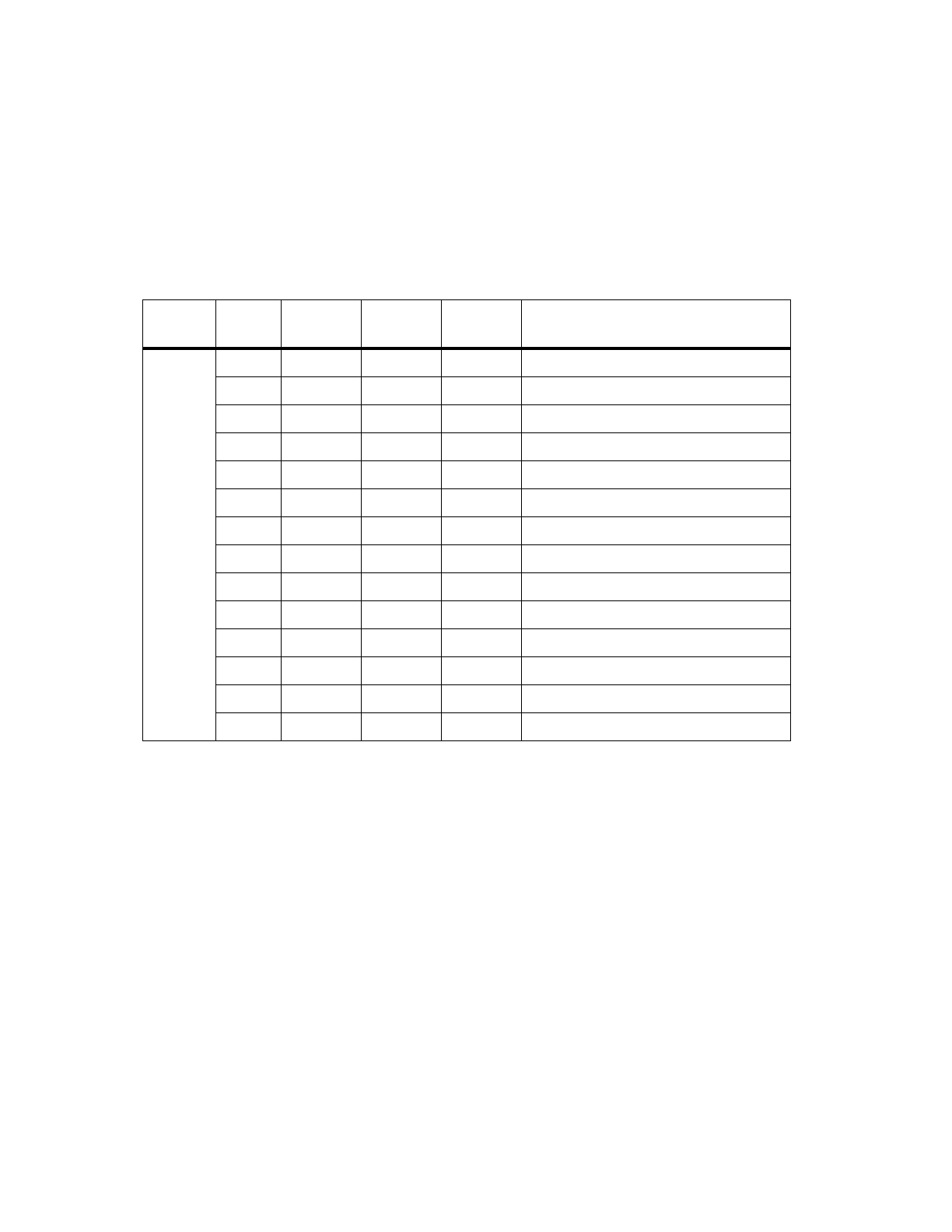

3.1.1 Machine State Register Contents after Reset

After all resets, all fields of the Machine State Register (MSR) contain zeros. Table 3-1 shows how

this affects core operation.

Table 3-1. MSR Contents after Reset

Register Field

Core

Reset

Chip

Reset

System

Reset Comment

MSR AP 0 0 0 APU unavailable

APE 0 0 0 Auxiliary processor exception disabled

WE 0 0 0 Wait state disabled

CE 0 0 0 Critical interrupts disabled

EE 0 0 0 External interrupts disabled

PR 0 0 0 Supervisor mode

FP 0 0 0 Floating point unavailable

ME 0 0 0 Machine check exceptions disabled

FE0 0 0 0 Floating point exception disabled

DWE 0 0 0 Debug wait mode disabled

DE 0 0 0 Debug interrupts disabled

FE1 0 0 0 Floating point exceptions disabled

DR 0 0 0 Data translation disabled

IR 0 0 0 Instruction translation disabled