5-26 PPC405 Core User’s Manual

is active. Therefore, insure that SRR0 and SRR1 are saved before enabling translation in an

interrupt handler.

5.21 Debug Interrupt

Debug interrupts can be either

synchronous

or

asynchronous

. These debug events generate

synchronous interrupts: branch taken (BT), data address compare (DAC), data value compare (DVC),

instruction address compare (IAC), instruction completion (IC), and trap instruction (TIE). The

exception (EXC) and unconditional (UDE) debug events generate asynchronous interrupts. See

“Debug Events” on page 8-10 for more information about debug events.

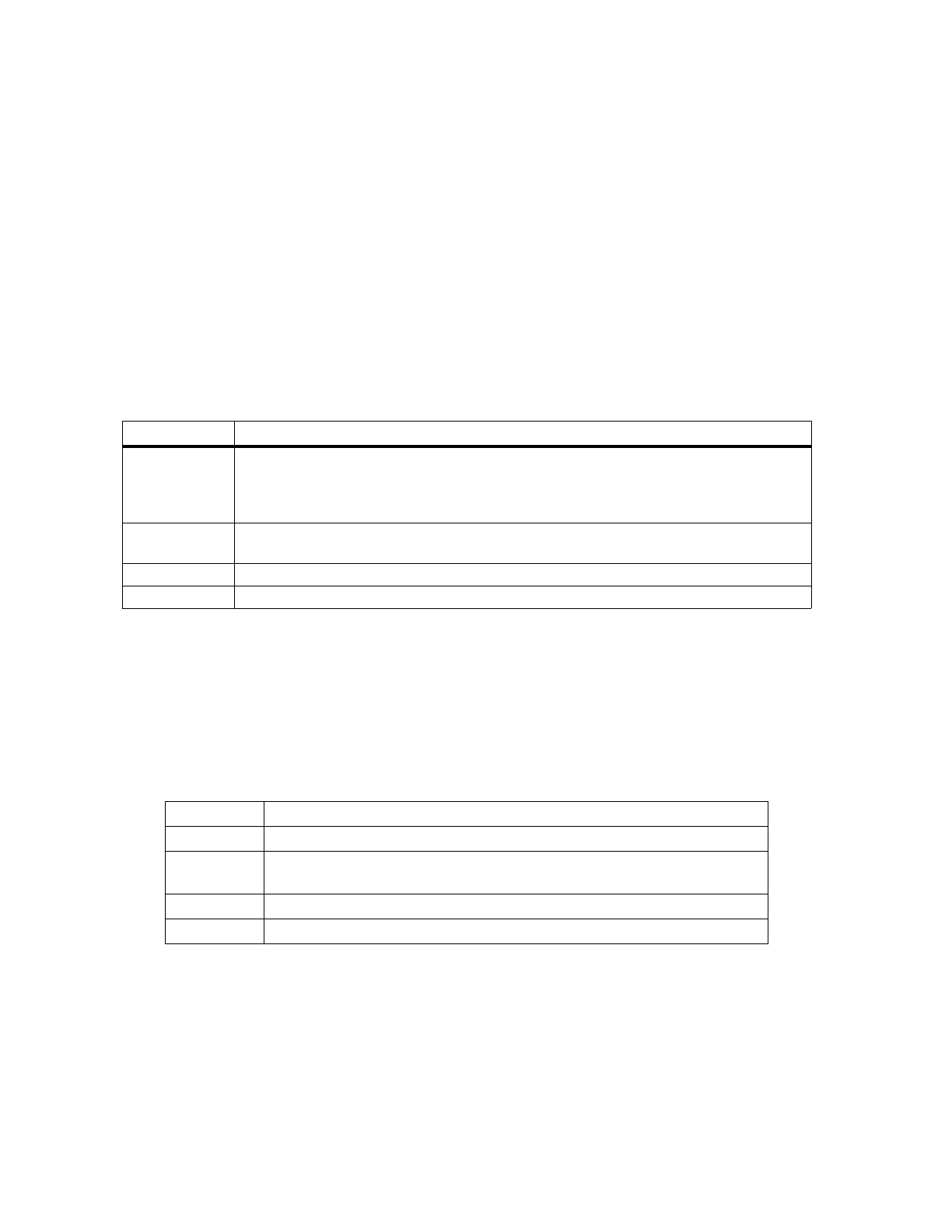

For debug events, SRR2 is written with an address, which varies with the type of debug event, as

shown in Table 5-22.

SRR3 is written with the contents of the MSR and the MSR is written with the values shown in

Table 5-23 on page 5-26. The high-order 16 bits of the program counter are then written with the

contents of the EVPR; the low-order 16 bits of the program counter are written with 0x2000. Interrupt

processing begins at the address in the program counter.

Executing an rfci instruction restores the program counter from SRR2 and the MSR from SRR3, and

execution resumes at the address in the program counter.

Table 5-22. SRR2 during Debug Interrupts

Debug Event Address Saved in SRR2

BT

DAC

IAC

TIE

Address of the instruction causing the event

DVC

IC

Address of the instruction

following

the instruction that causing the event

EXC Interrupt vector address of the initial exception that caused the exception debug event

UDE Address of next instruction to be executed at time of UDE

Table 5-23. Register Settings during Debug Interrupts

SRR2 Written with an address as described in Table 5-22

SRR3 Written with the contents of the MSR

MSR AP, APE, WE, CE, EE, PR, FP, FE0, DE, DWE, FE1, IR, DR ← 0

ME ← unchanged

PC EVPR[0:15] || 0x2000

DBSR Set to indicate type of debug event.