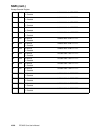

SRR2

Save/Restore Register 2

10-44 PPC405 Core User’s Manual

SRR2

SPR 0x3DE

See “Save/Restore Registers 2 and 3 (SRR2–SRR3)” on page 5-9.

.

Figure 10-28. Save/Restore Register 2 (SRR2)

0:29 SRR2 receives an instruction address when a critical interrupt is taken; the Program

Counter is restored from SRR2 when rfci executes.

30:31

Reserved

0 29 30 31