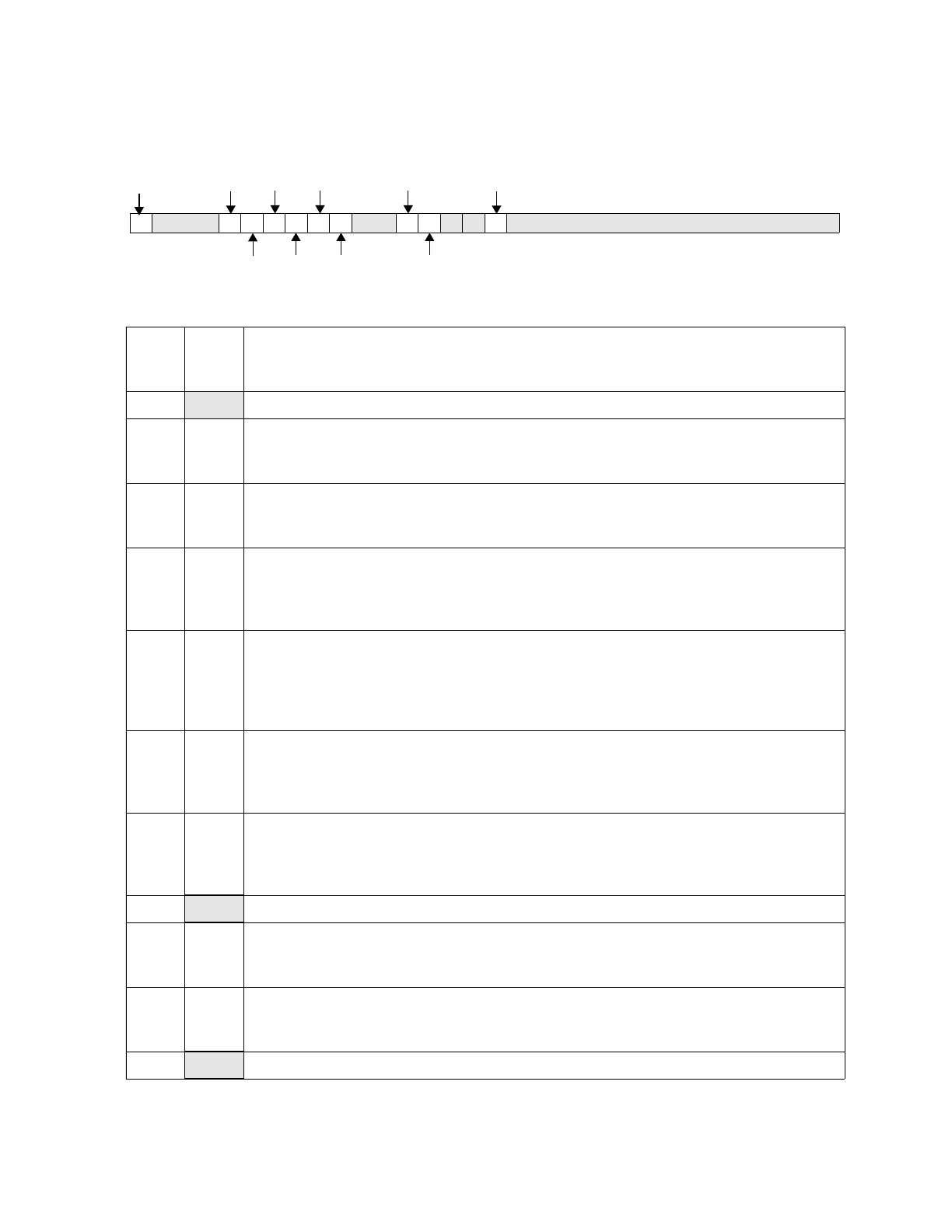

ESR

Exception Syndrome Register

Register Summary 10-23

ESR

SPR 0x3D4

See “Exception Syndrome Register (ESR)” on page 5-11.

Figure 10-12. Exception Syndrome Register (ESR)

0 MCI Machine check—instruction

0 Instruction machine check did not occur.

1 Instruction machine check occurred.

1:3

Reserved

4 PIL Program interrupt—illegal

0 Illegal Instruction error did not occur.

1 Illegal Instruction error occurred.

5 PPR Program interrupt—privileged

0 Privileged instruction error did not occur.

1 Privileged instruction error occurred.

6 PTR Program interrupt—trap

0 Trap with successful compare did not

occur.

1 Trap with successful compare occurred.

7

PEU Program interrupt—Unimplemented

0 APU/FPU unimplemented exception did

not occur.

1 APU/FPU unimplemented exception

occurred.

8 DST Data storage interrupt—store fault

0 Excepting instruction was not a store.

1 Excepting instruction was a store

(includes dcbi, dcbz, and dccci).

9 DIZ Data/instruction storage interrupt—zone

fault

0 Excepting condition was not a zone fault.

1 Excepting condition was a zone fault.

10:11

Reserved

12 PFP Program interrupt—FPU

0 FPU interrupt did not occur.

1 FPU interrupt occurred.

13

PAP Program interrupt—APU

0 APU interrupt did not occur.

1 APU interrupt occurred.

14:15

Reserved

0 1 345678910 11 12 13 14 15 16 17 31

MCI PIL

PPR

PTR

PEU DIZ

PFP

PAP

U0FDST