5-18 PPC405 Core User’s Manual

The following registers are modified to the specified values:

5.10 External Interrupt

External interrupts are triggered by active levels on the external interrupt inputs. All external

interrupting events are presented to the processor as a single external interrupt. External interrupts

are enabled or disabled by MSR[EE].

Programming Note: MSR[EE] also enables PIT and FIT interrupts. However, after timer

interrupts, control passes to different interrupt vectors than for the interrupts discussed in the

preceding paragraph. Therefore, these timer interrupts are described in “Programmable Interval

Timer (PIT) Interrupt” on page 5-22 and “Fixed Interval Timer (FIT) Interrupt” on page 5-23.

5.10.1 External Interrupt Handling

When MSR[EE] = 1 (external interrupts are enabled), a noncritical external interrupt occurs, and this

interrupt is the highest priority interrupt condition, the processor immediately writes the address of the

next sequential instruction into SRR0. Simultaneously, the contents of the MSR are saved in SRR1.

When the processor takes a noncritical external interrupt, MSR[EE] is set to 0. This disables other

external interrupts from interrupting the interrupt handler before SRR0 and SRR1 are saved. The

MSR is also written with the other values shown in Table 5-9 on page 5-19. The high-order 16 bits of

the program counter are written with the contents of the EVPR and the low-order 16 bits of the

program counter are written with 0x0500. Interrupt processing begins at the address in the program

counter.

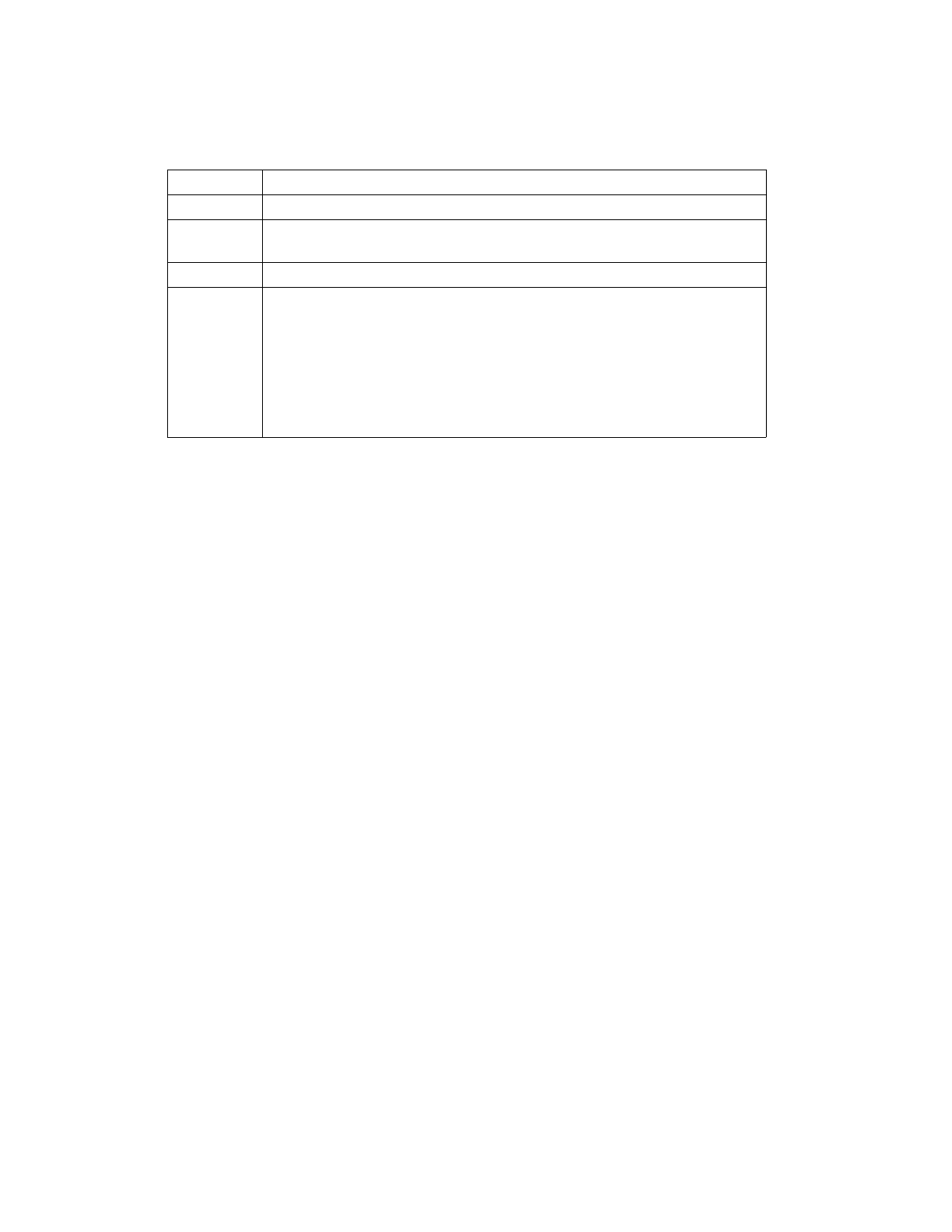

Table 5-8. Register Settings during Instruction Storage Interrupts

SRR0 Set to the EA of the instruction for which execute access was not permitted

SRR1 Set to the value of the MSR at the time of the interrupt

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged

PC EVPR[0:15] || 0x0400

ESR DIZ ← 1If access failure due to a zone protection fault (ZPR[Z

n

] = 00 in

user mode)

Note: If ESR[DIZ] is not set, the interrupt occurred because TBL_entry[EX]

was clear in an otherwise accessible zone, or because of an instruction

fetch from a storage region marked as guarded. See “Exception Syndrome

Register (ESR)” on page 5-11 for details of ESR operation.

MCI ← unchanged

All other bits are cleared.