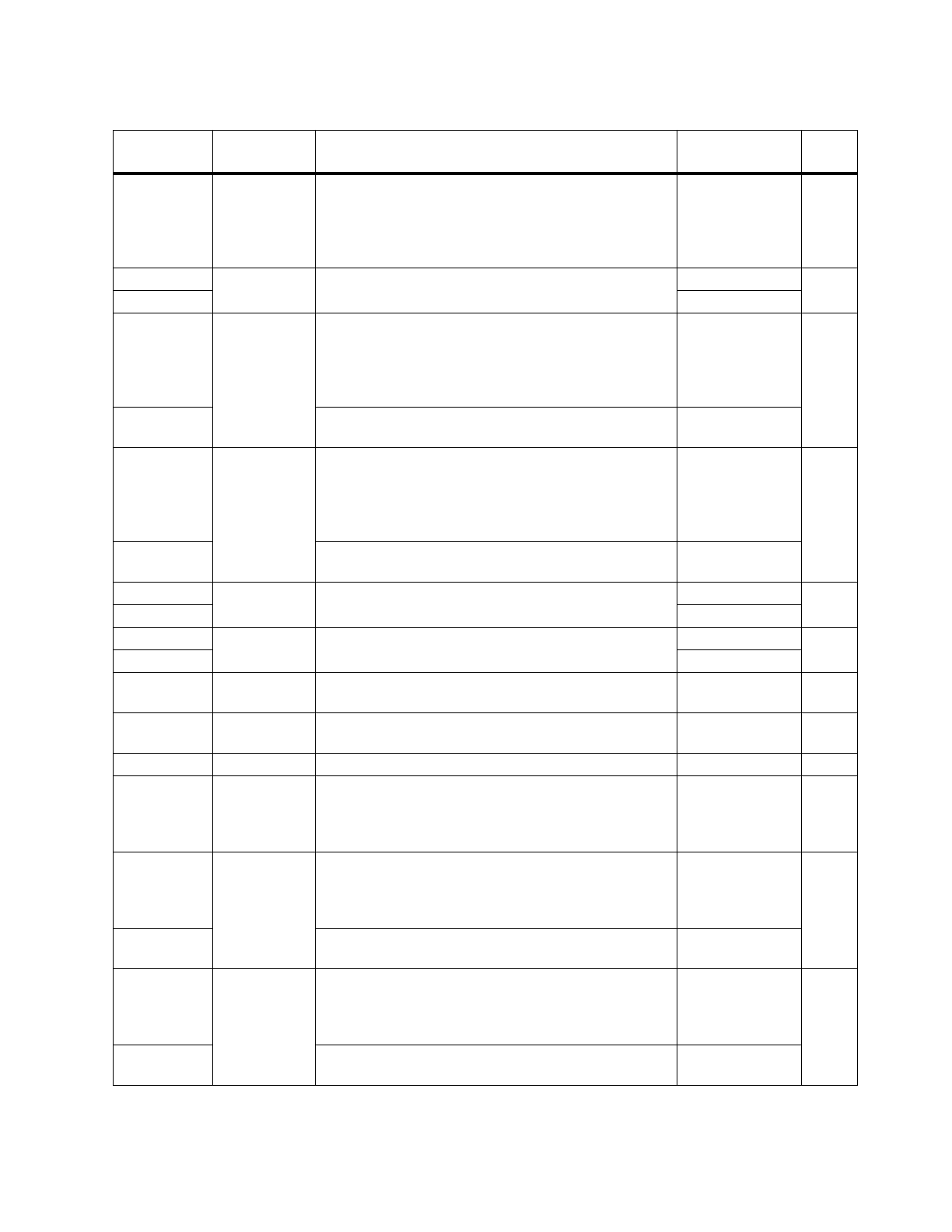

Instruction Summary A-15

eieio Storage synchronization. All loads and stores that

precede the eieio instruction complete before any

loads and stores that follow the instruction access

main storage.

Implemented as sync, which is more restrictive.

9-61

eqv RA, RS, RB Equivalence of (RS) with (RB).

(RA)

←¬((RS) ⊕ (RB))

9-62

eqv. CR[CR0]

extlwi RA, RS, n, b Extract and left justify immediate. (n > 0)

(RA)

0:n−1

← (RS)

b:b+n−1

(RA)

n:31

←

32−n

0

Extended mnemonic for

rlwinm RA,RS,b,0,n−1

9-60

extlwi.

Extended mnemonic for

rlwinm. RA,RS,b,0,n−1

CR[CR0]

extrwi RA, RS, n, b Extract and right justify immediate. (n > 0)

(RA)

32−n:31

← (RS)

b:b+n−1

(RA)

0:31−n

←

32−n

0

Extended mnemonic for

rlwinm RA,RS,b+n,32−n,31

9-147

extrwi.

Extended mnemonic for

rlwinm. RA,RS,b+n,32−n,31

CR[CR0]

extsb RA, RS Extend the sign of byte (RS)

24:31

.

Place the result in RA.

9-63

extsb. CR[CR0]

extsh RA, RS Extend the sign of halfword (RS)

16:31

.

Place the result in RA.

9-64

extsh. CR[CR0]

icbi RA, RB Invalidate the instruction cache block which contains

the effective address (RA|0) + (RB).

9-65

icbt RA, RB Load the instruction cache block which contains the

effective address (RA|0) + (RB).

9-66

iccci RA, RB Invalidate instruction cache. 9-67

icread RA, RB Read either tag or data information from the

instruction cache congruence class associated with

the effective address (RA|0) + (RB).

Place the results in ICDBDR.

9-68

inslwi RA, RS, n, b Insert from left immediate. (n > 0)

(RA)

b:b+n−1

← (RS)

0:n−1

Extended mnemonic for

rlwimi RA,RS,32−b,b,b+n−1

9-146

inslwi.

Extended mnemonic for

rlwimi. RA,RS,32−b,b,b+n−1

CR[CR0]

insrwi RA, RS, n, b Insert from right immediate. (n > 0)

(RA)

b:b+n−1

← (RS)

32−n:31

Extended mnemonic for

rlwimi RA,RS,32−b−n,b,b+n−1

9-146

insrwi.

Extended mnemonic for

rlwimi. RA,RS,32−b−n,b,b+n−1

CR[CR0]

Table A-1. PPC405 Instruction Syntax Summary (continued)

Mnemonic Operands Function

Other Registers

Changed Page