Fixed-Point Interrupts and Exceptions 5-5

5.4 Critical and Noncritical Interrupts

The PPC405 processes interrupts as noncritical and critical. The following interrupts are defined as

noncritical

: data storage, instruction storage, an active external interrupt input, alignment, program,

FPU unavailable, APU unavailable, system call, programmable interval timer (PIT), fixed interval timer

(FIT), data TLB miss, and instruction TLB miss. The following interrupts are defined as

critical

:

machine check interrupts (instruction- and data-side), debug interrupts, interrupts caused by an active

critical interrupt input, and the first time-out from the watchdog timer.

When a

noncritical

interrupt is taken, Save/Restore Register 0 (SRR0) is written with the address of

the excepting instruction (most synchronous interrupts) or the next sequential instruction to be

processed (asynchronous interrupts and system call).

If the PPC405 was executing a multicycle instruction (multiply, divide, or cache operation), the

instruction is terminated and its address is written in SRR0.

Aligned scalar loads/stores that are interrupted do not appear on the PLB. An aligned scalar

load/store cannot be interrupted after it is requested on the PLB, so the Guarded (G) storage attribute

does not need to prevent the interruption of an aligned scalar load/store.

To enhance performance, the DCU can respond to non-cachable load requests by retrieving a line

instead of a word. This is controlled by CCR0[LWL]. Note, however, that If CCR0[LWL] = 1, and the

target non-cachable region is also marked as guarded (the G storage attribute is set to 1), that the

DCU will request on the PLB only those bytes requested by the CPU.

Load/store multiples, load/store string, and misaligned scalar loads/stores that cross a word boundary

can be interrupted and restarted upon return from the interrupt handler.

When load instructions terminate, the addressing registers are not updated. This ensures that the

instructions can be restarted; if the addressing registers were in the range of registers to be loaded,

this would be an invalid form in any event. Some target registers of a load instruction may have been

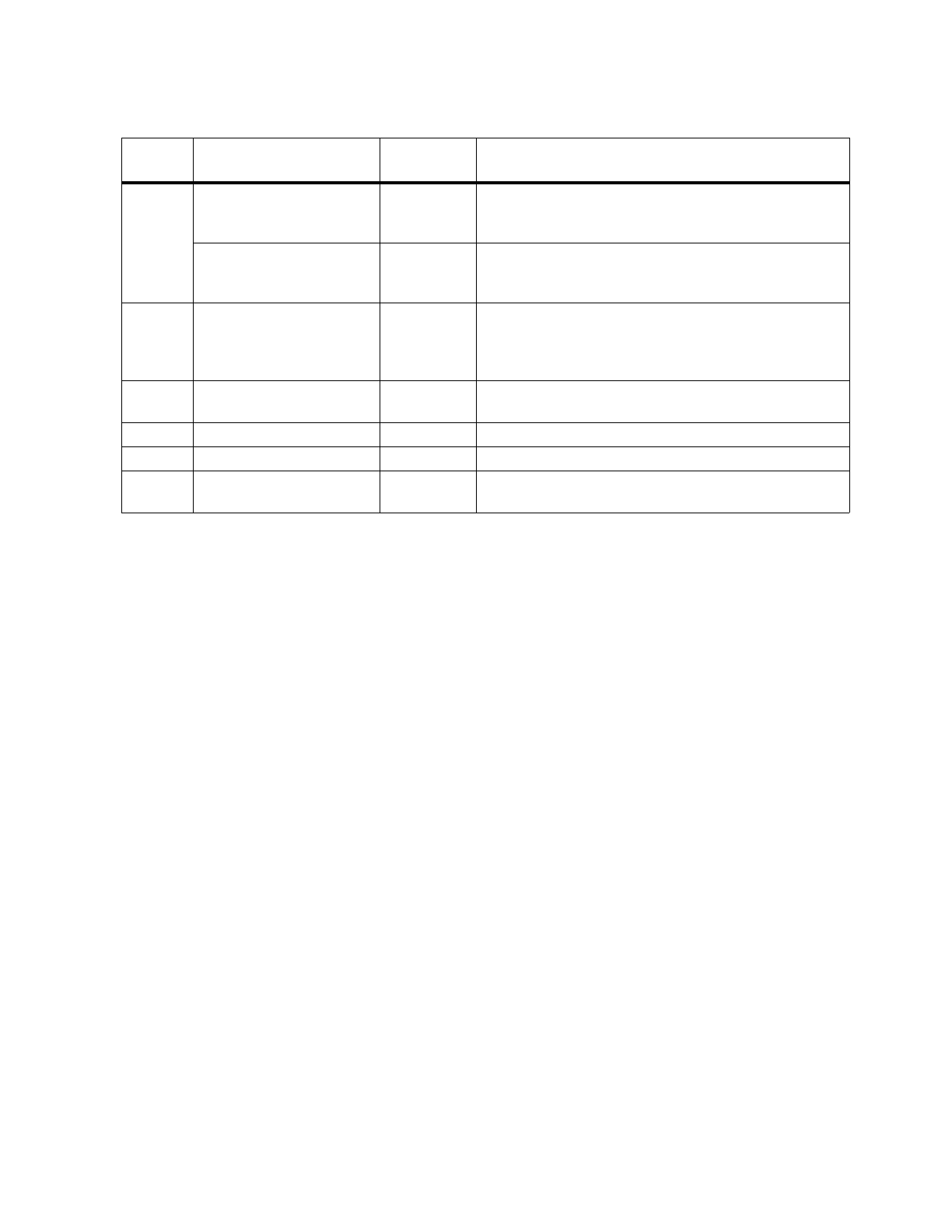

13 Data storage—

TLB_entry[WR] = 0

Noncritical Data translation is active and write access to the

translated address is not permitted because

TLB_entry[WR] = 0

Data storage—

TLB_entry[U0] = 1 or

SU0R[U

n

]=1

Noncritical Data translation is active and write access to the

translated address is not permitted because

TLB_entry[U0] = 1 or SU0R[U

n

]=1

14 Alignment Noncritical dcbz to non-cachable address or write-through

storage; non-word aligned dcread, lwarx, and stwcx,

as described in Table 5-10; misaligned APU or FPU

data access

15 Debug—BT, DAC, DVC,

IC, TIE

Critical BT, DAC, DVC, IC, TIE debug event (in internal debug

mode)

16 External interrupt input Noncritical Interrupts from the external interrupt input

17 Fixed Interval Timer (FIT) Noncritical Posting of an enabled FIT interrupt in the TSR

18 Programmable Interval

Timer (PIT)

Noncritical Posting of an enabled PIT interrupt in the TSR

Table 5-1. Interrupt Handling Priorities (continued)

Priority Interrupt Type

Critical or

Noncritical Causing Conditions