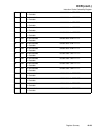

MSR

Machine State Register

10-32 PPC405 Core User’s Manual

MSR

See “Machine State Register (MSR)” on page 5-7.

Figure 10-19. Machine State Register (MSR)

0:5 Reserved

6 AP Auxiliary Processor Available

0 APU not available.

1 APU available.

7:11

Reserved

12 APE APU Exception Enable

0 APU exception disabled.

1 APU exception enabled.

13 WE Wait State Enable

0 The processor is not in the wait state.

1 The processor is in the wait state.

If MSR[WE] = 1, the processor remains in

the wait state until an interrupt is taken, a

reset occurs, or an external debug tool

clears WE.

14 CE Critical Interrupt Enable

0 Critical interrupts are disabled.

1 Critical interrupts are enabled.

Controls the critical interrupt input and

watchdog timer first time-out interrupts.

15

Reserved

16 EE External Interrupt Enable

0 Asynchronous interruptsare disabled.

1 Asynchronous interrupts are enabled.

Controls the non-critical external interrupt

input, PIT, and FIT interrupts.

17 PR Problem State

0 Supervisor state (all instructions

allowed).

1 Problem state (some instructions not

allowed).

18 FP Floating Point Available

0 The processor cannot execute floating-

point instructions

1 The processor can execute floating-point

instructions

19 ME Machine Check Enable

0 Machine check interrupts are disabled.

1 Machine check interrupts are enabled.

0 567 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 31

DE

CE

EE

IR

WE

PR

DRME

FP

FE0

FE1

DWE

AP

APE