Memory Management 7-3

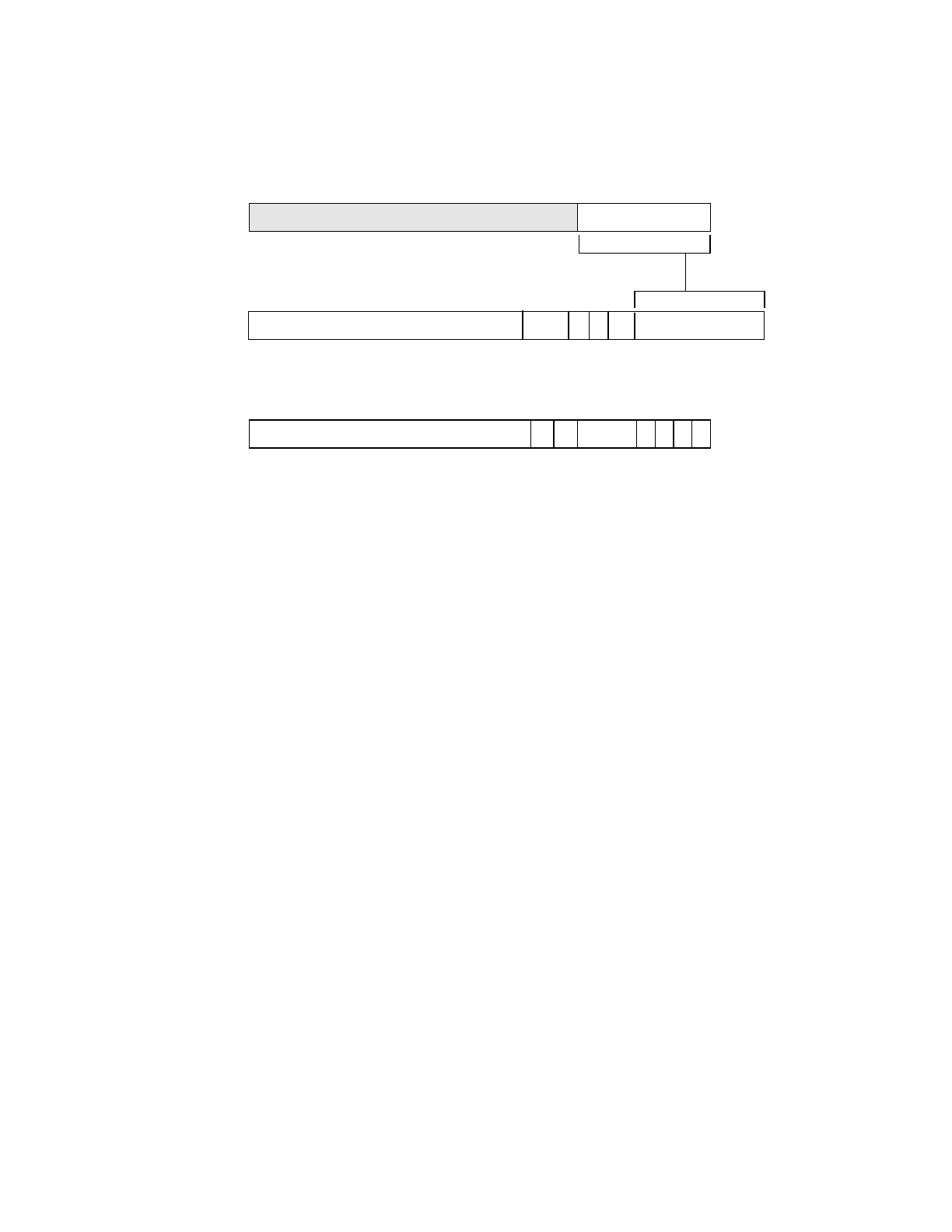

real page number (RPN), access control bits (ZSEL, EX, WR), and storage attributes (W, I, M, G, E,

U0

The virtual address space is extended by adding an 8-bit translation ID (TID) loaded from the Process

ID (PID) register during a TLB access. The PID identifies one of 255 unique software entities, usually

used as a process or thread ID. TLBHI[TID] is compared to the PID during a TLB look-up.

Tag and data entries are written by copying data from GPRs and the PID, using the tlbwe instruction.

Tag and data entries are read by copying data to GPRs and the PID, using the tlbre instruction.

Software can search for specific entries using the tlbsx instruction.

7.3.2 TLB Fields

Each TLB entry describes a page that is enabled for translation and access controls. Fields in the

TLB entry fall into four categories:

• Information required to identify the page to the hardware translation mechanism

• Control information specifying the translation

• Access control information

• Storage attribute control information

7.3.2.1 Page Identification Fields

When an EA is presented to the MMU for processing, the MMU applies several selection criteria to

each TLB entry to select the appropriate entry. Although it is possible to place multiple entries into the

TLB to match a specific EA and PID, this is considered a programming error, and the result of a TLB

lookup for such an EA is undefined. The following fields in the TLB entry identify the page. Except as

noted, all comparisons must succeed to validate an entry for subsequent use.

EPN (effective page number, 22 bits)

Compared to some number of the EA

0:21

bits presented to the MMU. The number of bits corresponds

to the page size.

0212224

ZSELRPN

TLBHI

0

SIZE

EPN

V

27 29 3 031

WI MGEX WR

TID

(Tag entry)

21 2522 35

28

24

23 28

PID

024

ID

31

(Process ID)

23

Figure 7-2. TLB Entries

TLBLO (Data entry)

26 27

E

U0