Fixed-Point Interrupts and Exceptions 5-13

occurred; the other ESR bits are set or cleared to indicate the other interrupt. These scenarios are

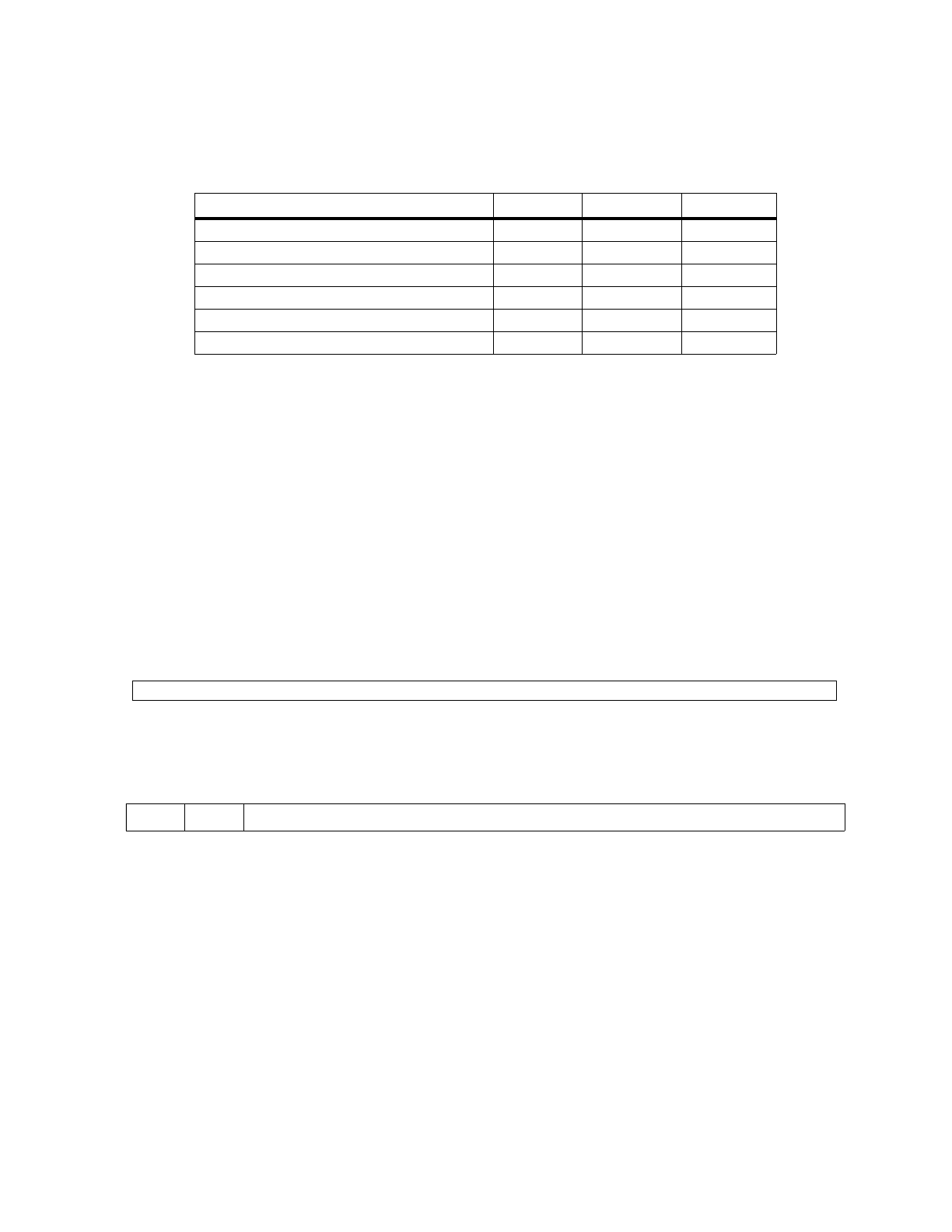

summarized in Table 5-3

Engineering Note: An implementation can use additional ESR bits to identify implementation-

specific exception types. Implementations can also use the ESR to record information about the

cause of a machine check interrupt.

5.5.6 Data Exception Address Register (DEAR)

The DEAR is a 32-bit register that contains the address of the access for which one of the following

synchronous precise errors occurred: alignment error, data TLB miss, or data storage interrupt.

The contents of the DEAR can be written to a GPR using the mfspr instruction. The contents of a

GPR can be written to the DEAR using the mtspr instruction.

Figure 5-8 shows the DEAR bit definitions.

5.6 Critical Input Interrupts

An external source requests a critical interrupt by driving the critical interrupt input active. The critical

interrupt is recognized if enabled by MSR[CE].

MSR[CE] also enables the watchdog timer first-time-out interrupt. However, the watchdog interrupt

has a different interrupt vector than the critical pin interrupt. See “Watchdog Timer Interrupt” on

page 5-24.

After detecting a critical interrupt, if no synchronous precise interrupts are outstanding, the PPC405

immediately takes the critical interrupt and writes the address of the next instruction to be executed in

Table 5-3. ESR Alteration by Various Interrupts

Scenario ECR[MCI] ESR

4:7, 1213

ESR

8:9, 16

Program interrupt Unchanged Set to type Cleared

Data storage interrupt Unchanged Cleared Set to Type

Data TLB miss interrupt Unchanged Cleared Cleared

Machine check—instruction Set to 1 Cleared Cleared

Disabled MCI, no others Unchanged Unchanged Unchanged

Disabled MCI and program interrupt Unchanged Set to type Cleared

Figure 5-8. Data Exception Address Register (DEAR)

0:31 Address of Data Error (synchronous)

0 31