Programming Model 2-41

2.11.6.3 Shift Instructions

These instructions rotate operands stored in the GPRs.

Table 2-20 lists the PPC405 shift instructions. Shift right algebraic instructions implicitly update

XER[CA]. In the table, the syntax “[.]” indicates that the instruction has a “record” form that updates

CR[CR0], and a “non-record” form.

2.11.6.4 Cache Management Instructions

These instructions control the operation of the ICU and DCU. Instructions are provided to fill or

invalidate instruction cache blocks. Instructions are also provided to fill, flush, invalidate, or zero data

cache blocks, where a block is defined as a 32-byte cache line.

Table 2-21 lists the PPC405 core cache management instructions.

2.11.7 Interrupt Control Instructions

mfmsr and mtmsr read and write data between the MSR and a GPR to enable and disable

interrupts. wrtee and wrteei enable and disable external interrupts. rfi and rfci return from interrupt

handlers. Table 2-22 lists the PPC405 core interrupt control instructions.

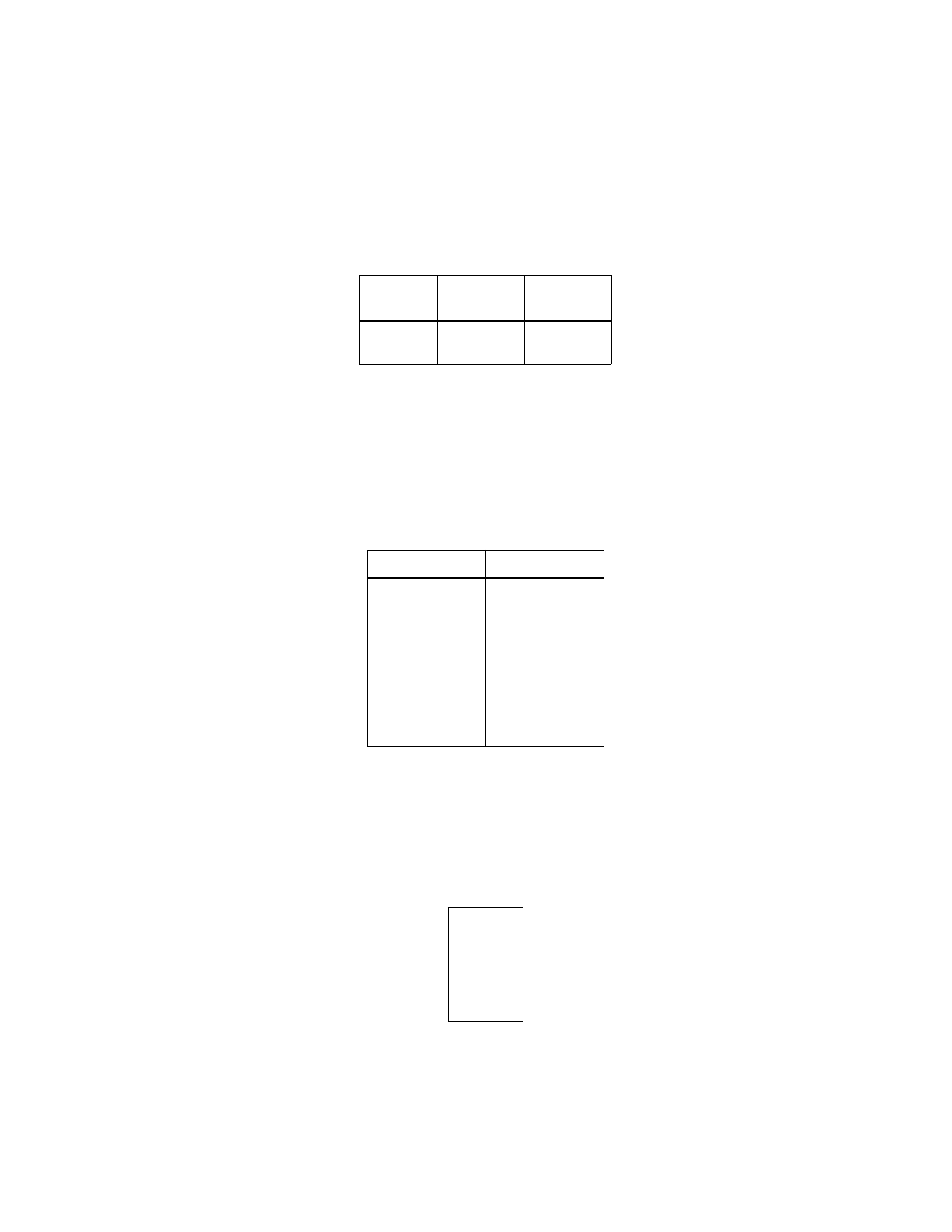

Table 2-20. Shift Instructions

Shift Left Shift Right

Shift Right

Algebraic

slw[.] srw[.] sraw[.]

srawi[.]

Table 2-21. Cache Management Instructions

DCU ICU

dcba

dcbf

dcbi

dcbst

dcbt

dcbtst

dcbz

dccci

dcread

icbi

icbt

iccci

icread

Table 2-22. Interrupt Control Instructions

mfmsr

mtmsr

rfi

rfci

wrtee

wrteei