Fixed-Point Interrupts and Exceptions 5-15

handler (EVPR[0:15] || 0x0200), setting ESR[MCI]. Note that only a bus error can cause a machine

check—instruction interrupt. Taking the vector automatically clears MSR[ME] and the other MSR

fields.

Note that it is improper to declare a machine check—instruction interrupt when the instruction is

fetched, because the address is possibly the result of an incorrect speculation by the fetcher. It is

quite likely that no attempt will be made to execute an instruction from the erroneous address. The

interrupt will occur only if execution of the instruction is subsequently attempted.

When a machine check occurs on an instruction fetch, the erroneous instruction is never validated in

the instruction cache unit (ICU). Fetch requests to cachable memory that miss in the ICU cause an

instruction cache line fill (eight words). If any words in the fetched line are associated with an error, an

interrupt occurs upon attempted execution and the cache line is invalidated. If any word in the line is

in error, the cache line is invalidated after the line fill.

ESR[MCI] is set, even if MSR[ME] = 0. This means that if a machine check—instruction interrupt

occurs while running in code in which MSR[ME] is disabled, the machine check—instruction interrupt

is recorded in the ESR, but no interrupt occurs. Software running with MSR[ME] disabled can sample

ESR[MCI] to determine whether at least one machine check—instruction interrupt occurred during

the disabled execution.

If a new machine check—instruction interrupt occurs after MSR[ME] is enabled again, the new

machine check—instruction interrupt is recorded in ESR[MCI] and the machine check—instruction

interrupt handler is invoked. However, enabling MSR[ME] again does

not

cause a machine Check

interrupt to occur simply due to the presence of ESR[MCI] indicating that a machine check—

instruction interrupt occurred while MSR[ME] was disabled. The machine check—instruction interrupt

must occur while MSR[ME] is enabled for the machine check interrupt to be taken. Software should,

in general, clear the ESR bits before returning from a machine check interrupt to avoid any ambiguity

when handling subsequent machine check interrupts.

5.7.2 Data Machine Check Handling

When a machine check occurs on an data access, a machine check—data interrupt occurs. The

handling of machine check—data interrupts is implementation-specific.

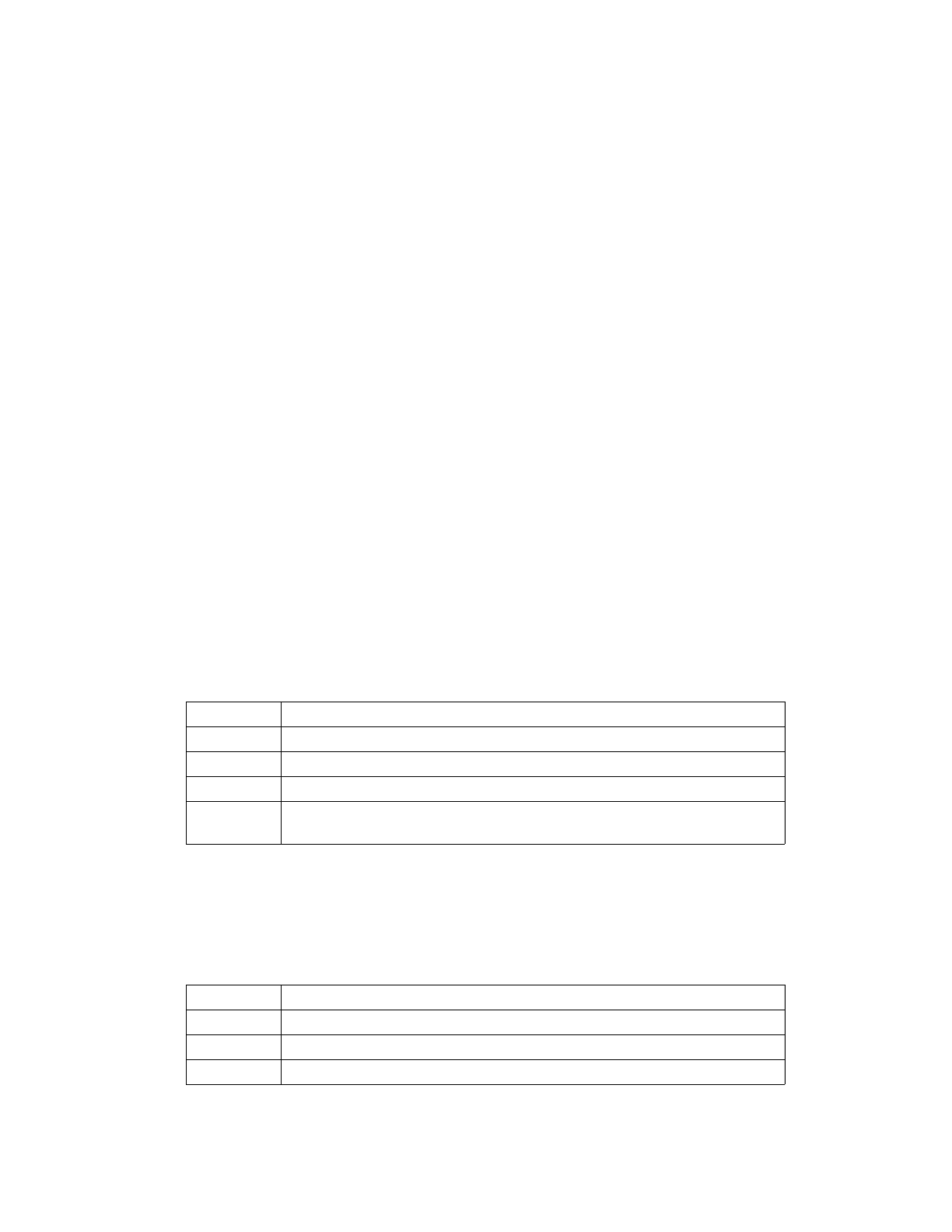

Table 5-5. Register Settings during Machine Check—Instruction Interrupts

SRR2 Written with the address that caused the machine check.

SRR3 Written with the contents of the MSR

MSR WE, CE, EE, PR, ME, FP, FE0, DWE, DE, FE1, IR, DR←0

PC EVPR[0:15] || 0x0200

ESR MCI ← 1

All other bits are cleared.

Table 5-6. Register Settings during Machine Check—Data Interrupts

SRR2 Written with the address of the next sequential instruction.

SRR3 Written with the contents of the MSR

MSR WE, CE, EE, PR, ME, FP, FE0, DWE, DE, FE1, IR, DR←0

PC EVPR[0:15] || 0x0200