Memory Management 7-9

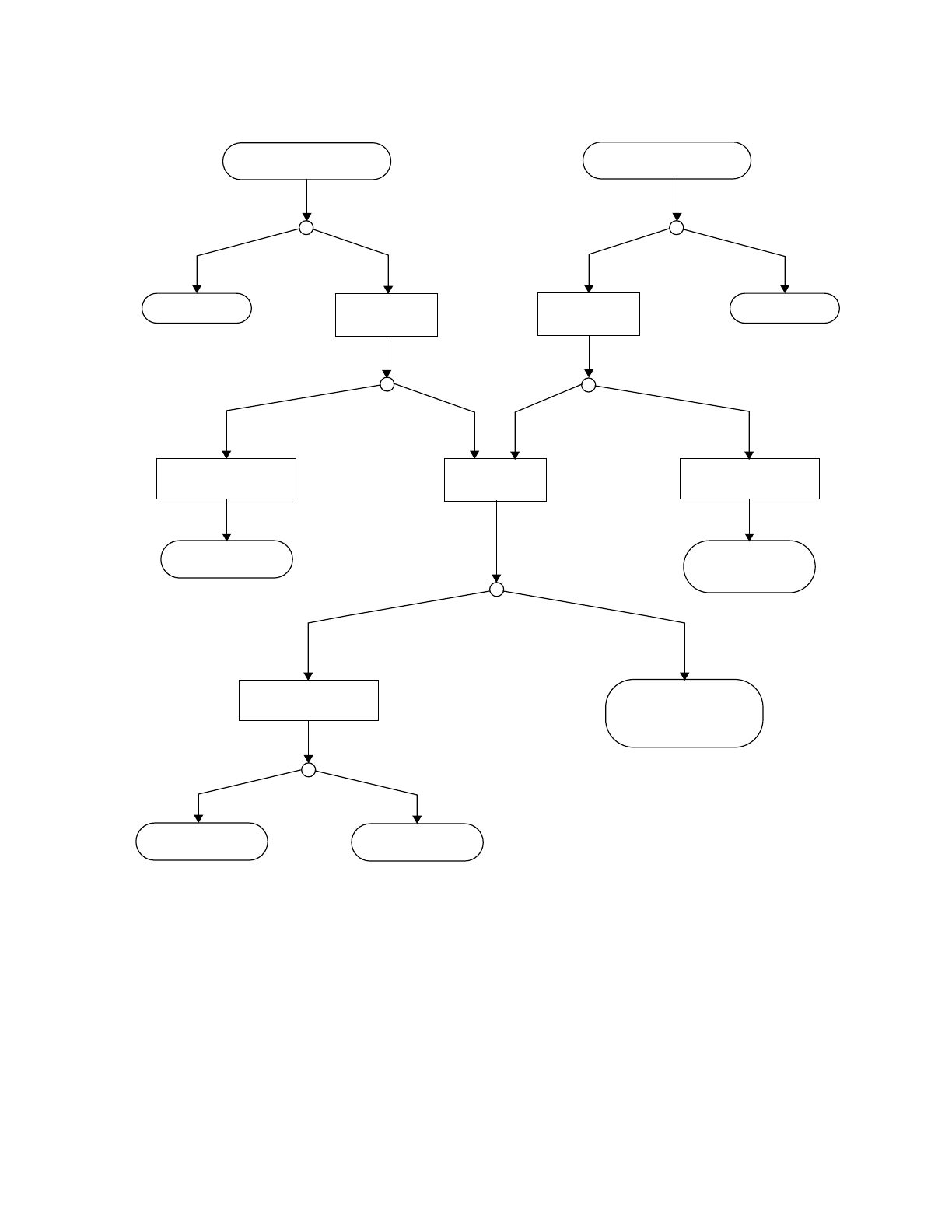

Figure 7-3 illustrates the relationship of the shadow TLBs and UTLB in address translation:

7.4 TLB-Related Interrupts

The processor relies on interrupt handling software to implement paged virtual memory, and to

enforce protection of specified memory pages.

When an interrupt occurs, the processor clears MSR[IR, DR]. Therefore, at the start of all interrupt

handlers, the processor operates in real mode for instruction accesses and data accesses. Note that

when address translation is disabled for an instruction fetch or load/store, the EA is equal to the real

Figure 7-3. ITLB/DTLB/UTLB Address Resolution

Generate I-side

Effective Address

Extract Real

Address from ITLB

Continue I-cache

Access

Perform ITLB

Look-up

Translation Disabled

(MSR[IR]=0)

Translation Enabled

(MSR[IR] = 1)

I-Side TLB Miss

or

D-Side TLB Miss

No Translation

Translation Enabled

(MSR[DR] = 1)

Translation Disabled

(MSR[DR] = 0)

No Translation

Generate D-side

Effective Address

Perform DTLB

Look-up

ITLB MissITLB Hit

Perform UTLB

Look-up

DTLB Miss DTLB Hit

Extract Real

Address from UTLB

Access

Continue I-cache

or D-cache

Access

UTLB MissUTLB Hit

Extract Real

Address from DTLB

Route Address

to ITLB

Route Address

to DTLB

Exception