Instruction Set 9-191

tw

Trap Word

(SRR0)

← address of tw instruction

(SRR1)

← (MSR)

(ESR[PTR])

← 1

(DBSR[TIE,IDE])

← 1,1

(MSR[WE, EE, PR, DR, IR])

← 0

PC

← EVPR

0:15

|| 0x0700

If instruction bit 31 contains 1, the contents of CR[CR0] are undefined.

Registers Altered

• None

Invalid Instruction Forms

• Reserved fields

Programming Note

This instruction is inserted into the execution stream by a debugger to implement breakpoints, and is

not typically used by application code.

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

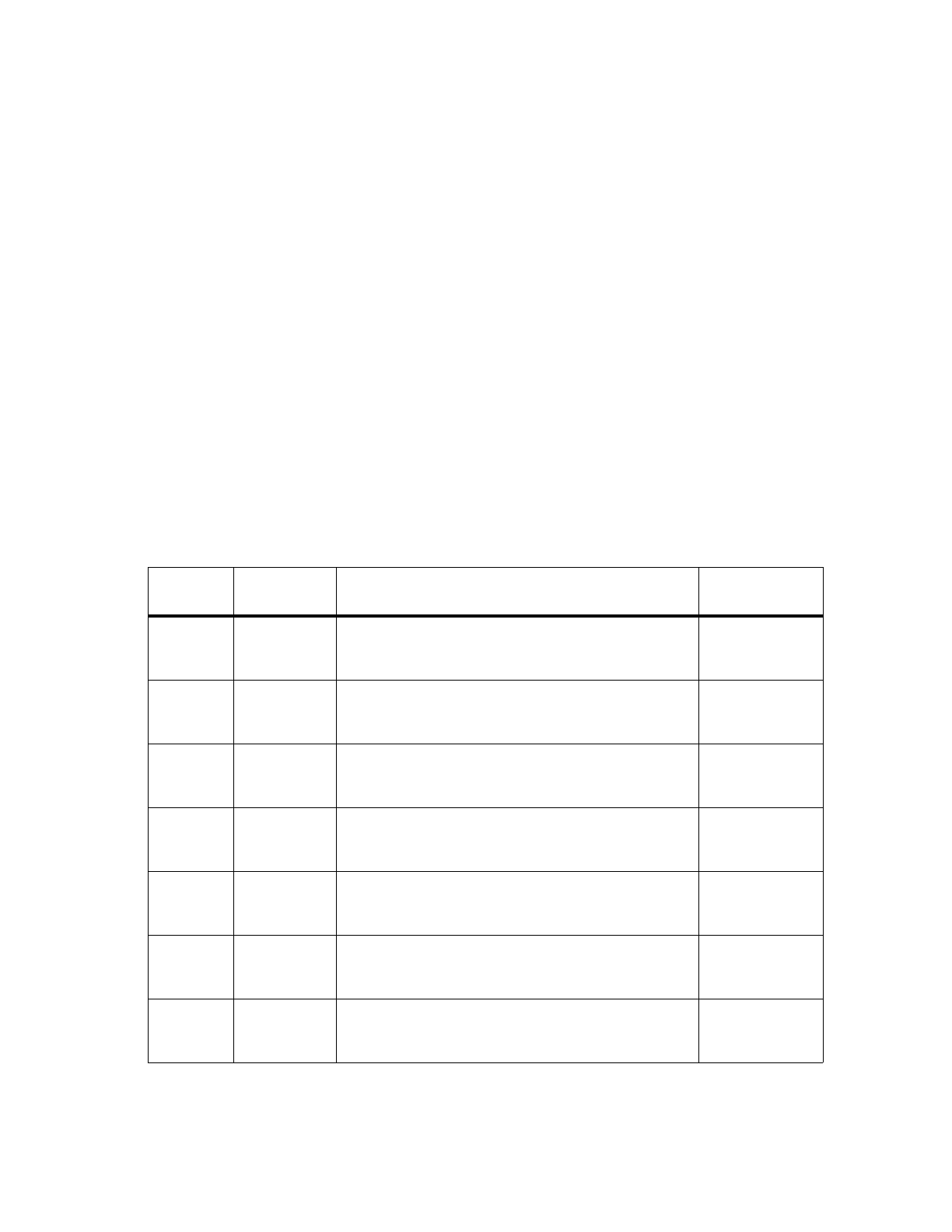

Table 9-34. Extended Mnemonics for tw

Mnemonic Operands Function

Other Registers

Altered

trap Trap unconditionally.

Extended mnemonic for

tw 31,0,0

tweq RA, RB Trap if (RA) equal to (RB).

Extended mnemonic for

tw 4,RA,RB

twge RA, RB Trap if (RA) greater than or equal to (RB).

Extended mnemonic for

tw 12,RA,RB

twgt RA, RB Trap if (RA) greater than (RB).

Extended mnemonic for

tw 8,RA,RB

twle RA, RB Trap if (RA) less than or equal to (RB).

Extended mnemonic for

tw 20,RA,RB

twlge RA, RB Trap if (RA) logically greater than or equal to (RB).

Extended mnemonic for

tw 5,RA,RB

twlgt RA, RB Trap if (RA) logically greater than (RB).

Extended mnemonic for

tw 1,RA,RB