Instructions by Category B-5

B.2 Instructions in the IBM PowerPC Embedded Environment

To meet the functional requirements of processors for embedded systems and real-time applications,

the IBM PowerPC Embedded Environment defines instructions that are not part of the PowerPC

Architecture.

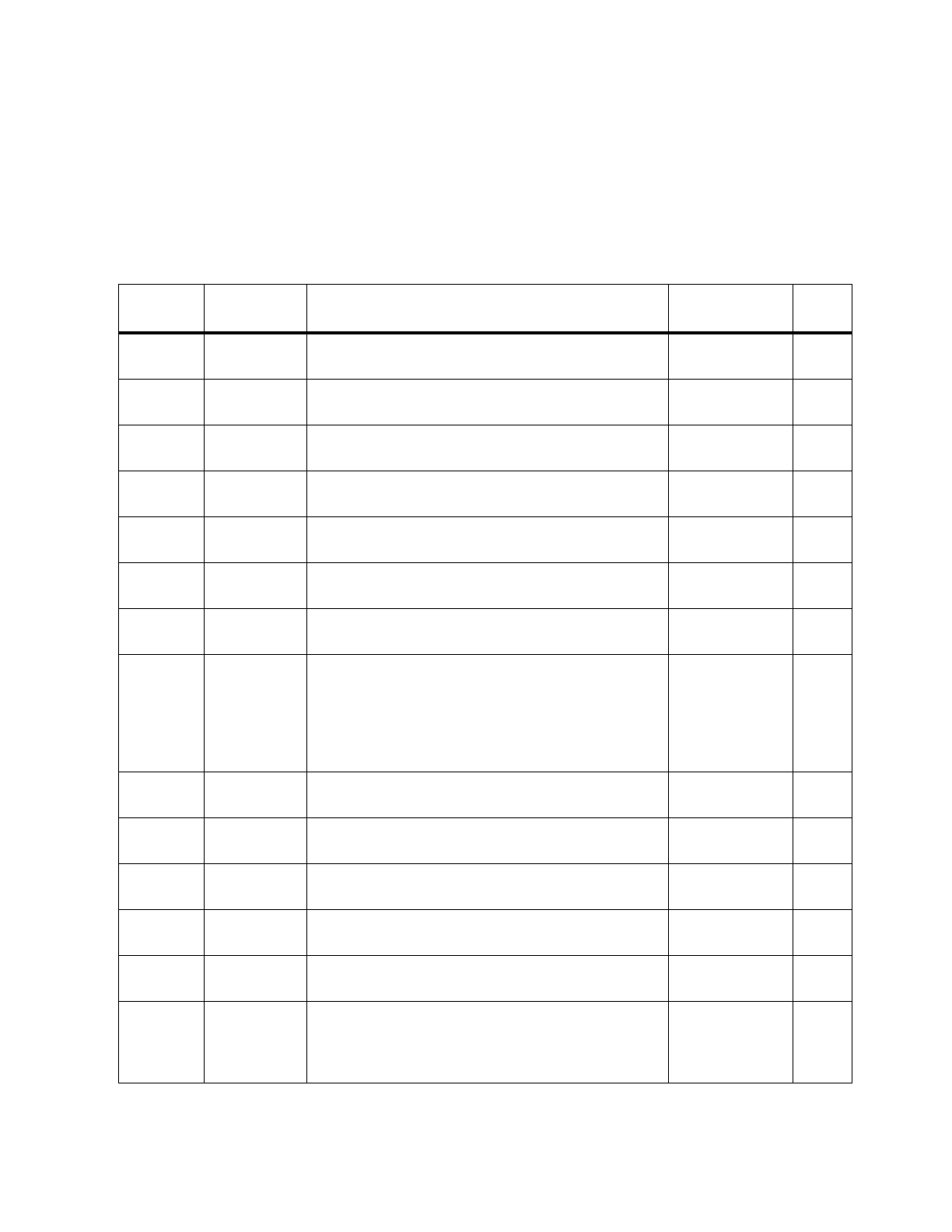

Table B-3 summarizes the PPC405 core instructions in the PowerPC Embedded Environment.

Table B-3. Instructions in the IBM PowerPC Embedded Environment

Mnemonic Operands Function

Other Registers

Changed Page

dcba RA, RB Speculatively establish the data cache block which

contains the EA (RA|0) + (RB).

9-47

dcbf RA, RB Flush (store, then invalidate) the data cache block

which contains the EA (RA|0) + (RB).

9-49

dcbi RA, RB Invalidate the data cache block which contains the EA

(RA|0) + (RB).

9-50

dcbst RA, RB Store the data cache block which contains the EA

(RA|0) + (RB).

9-50

dcbt RA, RB Load the data cache block which contains the EA

(RA|0) + (RB).

9-52

dcbtst RA,RB Load the data cache block which contains the EA

(RA|0) + (RB).

9-53

dcbz RA, RB Zero the data cache block which contains the EA

(RA|0) + (RB).

9-54

eieio Storage synchronization. All loads and stores that

precede the eieio instruction complete before any

loads and stores that follow the instruction access

main storage.

Implemented as sync, which is more restrictive.

9-61

icbi RA, RB Invalidate the instruction cache block which contains

the EA (RA|0) + (RB).

9-65

icbt RA, RB Load the instruction cache block which contains the

EA (RA|0) + (RB).

9-66

isync Synchronize execution context by flushing the

prefetch queue.

9-70

mfdcr RT, DCRN Move from DCR to RT,

(RT)

← (DCR(DCRN)).

9-110

mfmsr RT Move from MSR to RT,

(RT)

← (MSR).

9-111

mfspr RT, SPRN Move from SPR to RT,

(RT)

← (SPR(SPRN)).

Privileged for all SPRs except

LR, CTR, TBHU, TBLU, and XER.

9-112