Debugging 8-21

1. A 10K ohm pullup resistor should be connected to this signal to reduce chip power consumption.

The pullup resistor is not required.

2. The +POWER signal, sourced from the target development board, indicates whether the processor

is operating. This signal does not supply power to the RISCWatch hardware or to the processor.

The active level on this signal can be +5V or +3.3V (note that the PPC405 core can have either

+5V or +3.3V I/O, but the processor itself must be powered by +3.3V). A series resistor (1K ohm or

less) should be used to provide short circuit current-limiting protection.

3. A 10K ohm pullup resistor must be connected to these signals to ensure proper chip operation

when these inputs are not used.

8.7.1 JTAG Instructions

The JTAG debug port provides the standard

extest

,

idcode

,

sample/preload

, and

bypass

instructions

and the optional

highz

and

clamp

instructions. Invalid instructions behave as the

bypass

instruction.

8.7.2 JTAG Boundary Scan

Boundary Scan Description Language (BSDL), IEEE 1149.1b-1994, is a supplement to IEEE

1149.1-1990 and IEEE 1149.1a-1993

Standard Test Access Port and Boundary-Scan Architecture

.

BSDL, a subset of the IEEE 1076-1993 Standard VHSIC Hardware Description Language (VHDL),

allows a rigorous description of testability features in components which comply with the standard.

BSDL is used by automated test pattern generation tools for package interconnect tests and by

electronic design automation (EDA) tools for synthesized test logic and verification. BSDL supports

9 I TMS

1

JTAG Test Mode Select

10

NC Reserved

11

I HALT

3

Processor Halt

12

NC Reserved

13

NC Reserved

14

Key The pin at this position should be removed.

15

NC Reserved

16

GND Ground

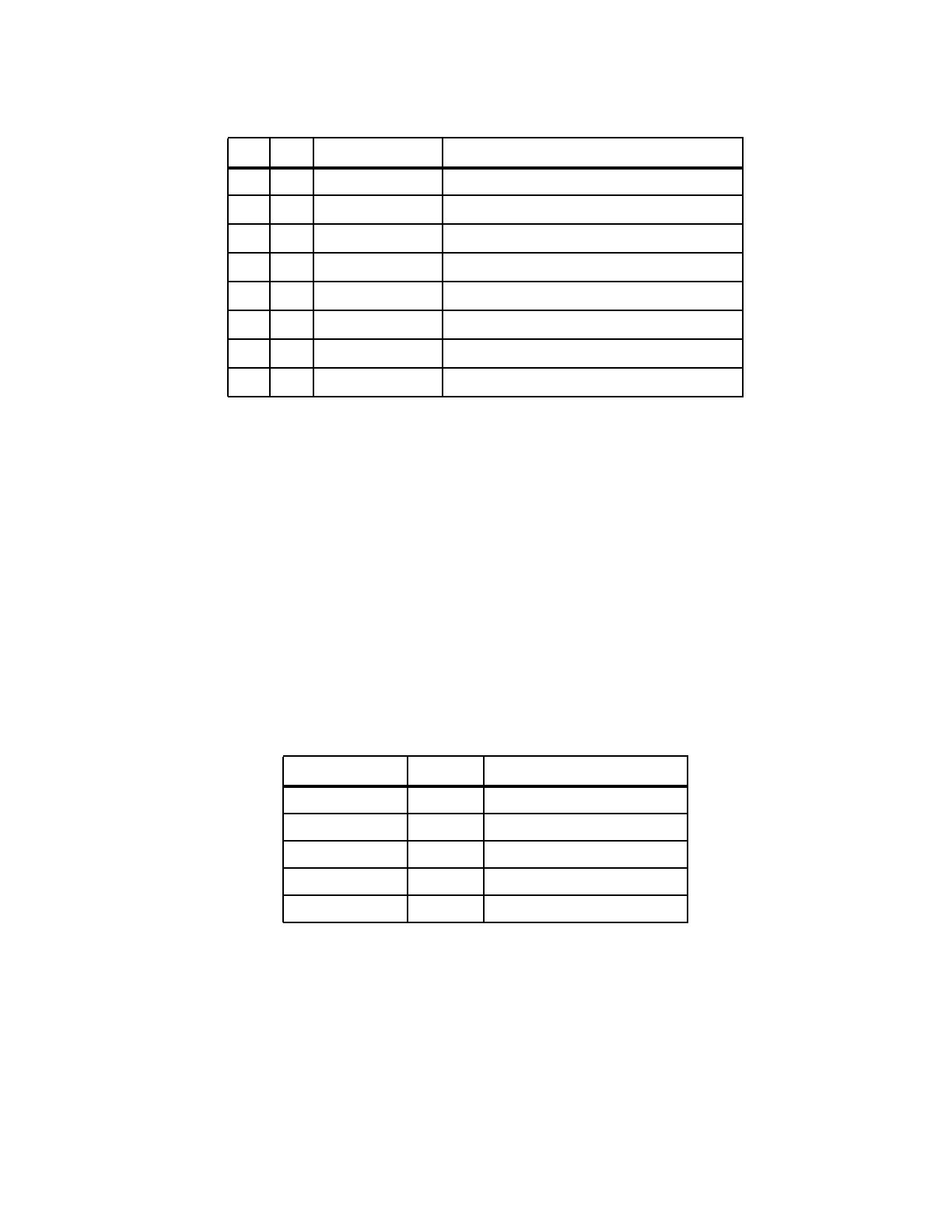

Table 8-8. JTAG Instructions

Instruction Code Comments

Extest 000 IEEE 1149.1 standard.

Intest 1111001 IEEE 1149.1 standard.

Sample/Preload 1111010 IEEE 1149.1 standard.

Private xxxx100 Private instructions

Bypass 1111111 IEEE 1149.1 standard.

Table 8-7. JTAG Connector Signals (continued)

Pin I/O Signal Description