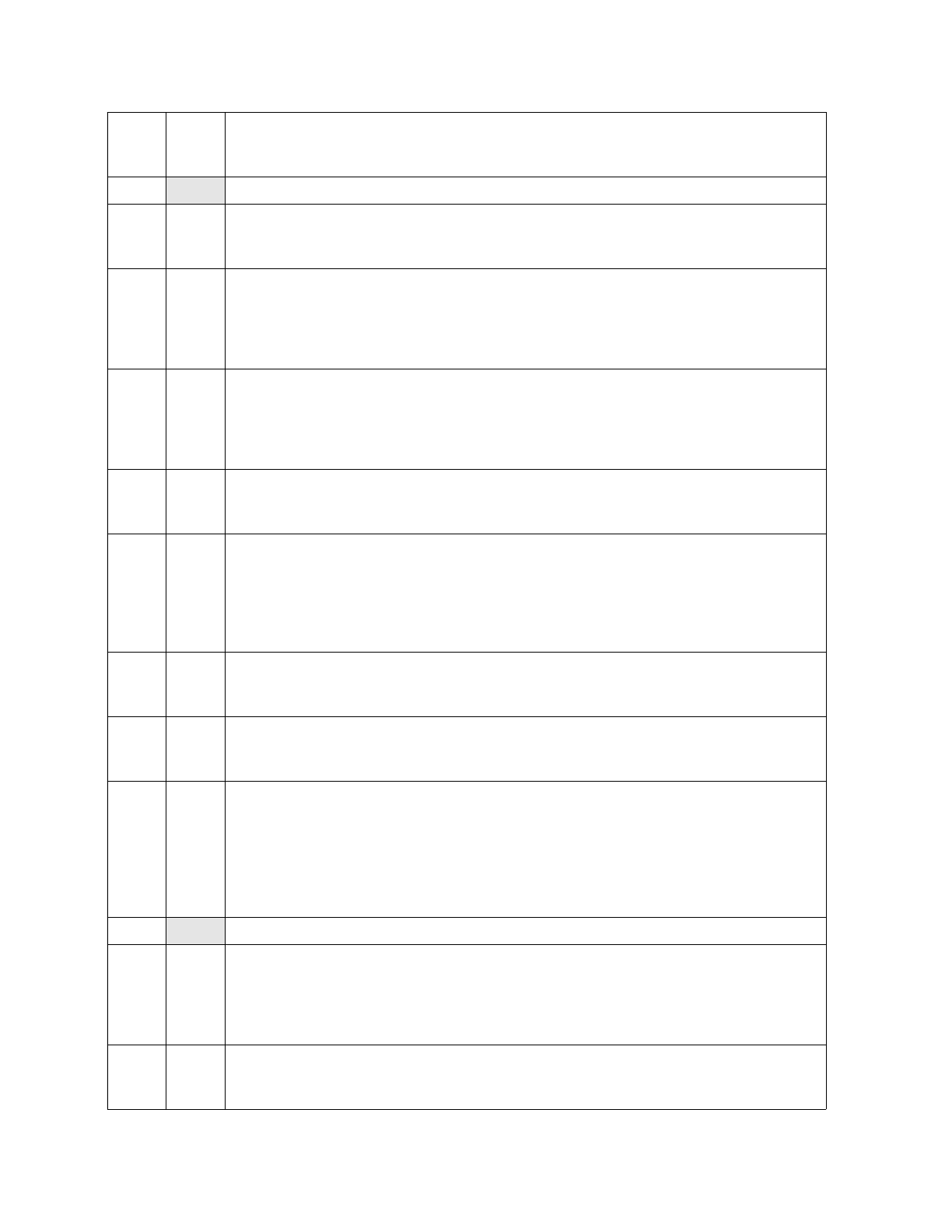

5-8 PPC405 Core User’s Manual

14 CE Critical Interrupt Enable

0 Critical interrupts are disabled.

1 Critical interrupts are enabled.

Controls the critical interrupt input and

watchdog timer first time-out interrupts.

15

Reserved

16 EE External Interrupt Enable

0 Asynchronous interruptsare disabled.

1 Asynchronous interrupts are enabled.

Controls the non-critical external interrupt

input, PIT, and FIT interrupts.

17 PR Problem State

0 Supervisor state (all instructions

allowed).

1 Problem state (some instructions not

allowed).

18 FP Floating Point Available

0 The processor cannot execute floating-

point instructions

1 The processor can execute floating-point

instructions

19 ME Machine Check Enable

0 Machine check interrupts are disabled.

1 Machine check interrupts are enabled.

20 FE0 Floating-point exception mode 0

0 If MSR[FE1] = 0, ignore exceptions

mode; if MSR[FE1] = 1, imprecise

nonrecoverable mode

1 If MSR[FE1] = 0, imprecise recoverable

mode; if MSR[FE1] = 1, precise mode

21 DWE Debug Wait Enable

0 Debug wait mode is disabled.

1 Debug wait mode is enabled.

22 DE Debug Interrupts Enable

0 Debug interrupts are disabled.

1 Debug interrupts are enabled.

23 FE1 Floating-point exception mode 1

0 If MSR[FE0] = 0, ignore exceptions

mode; if MSR[FE0] = 1, imprecise

recoverable mode

1 If MSR[FE0] = 0, imprecise non-

recoverable mode; if MSR[FE0] = 1,

precise mode

24:25

Reserved

26 IR Instruction Relocate

0 Instruction address translation is

disabled.

1 Instruction address translation is

enabled.

27 DR Data Relocate

0 Data address translation is disabled.

1 Data address translation is enabled.