Debugging 8-9

8.5.3 Instruction Address Compare Registers (IAC1–IAC4)

The PPC405 can take a debug event upon an attempt to execute an instruction from an address. The

address, which must be word-aligned, is defined in an IAC register. The DBCR0[IA1, IA2] fields of

DBCR0 controls the instruction address compare (IAC) debug event.

8.5.4 Data Address Compare Registers (DAC1–DAC2)

The PPC405 can take a debug event upon storage or cache references to addresses specified in the

DAC registers. The specified addresses in the DAC registers are EAs of operands of storage

references or cache instructions.The fields DBCR1[D1R], [D2R] and DBCR[D1W], [D2W] control the

DAC-read and DAC-write debug events, respectively.

Addresses in the DAC registers specify exact byte EAs for DAC debug events. However, one may

want to take a debug event on any byte within a halfword (ignore the least significant bit (LSb) of the

DAC), on any byte within a word (ignore the two LSbs of DAC), or on any byte within eight words

(ignore four LSbs of DAC). DBCR1[D1S, D2S] control the addressing options.

Errors related to execution of storage reference or cache instructions prevent DAC debug events.

12 IA3 IAC3 Debug Event

0 Event did not occur

1 Event occurred

13 IA4 IAC4 Debug Event

0 Event did not occur

1 Event occurred

14:21

Reserved

22:23 MRR Most Recent Reset

00 No reset has occurred since last

cleared by software.

01 Core reset

10 Chip reset

11 System reset

This field is set to a value, indicating the

type of reset, when a reset occurs.

24:31

Reserved

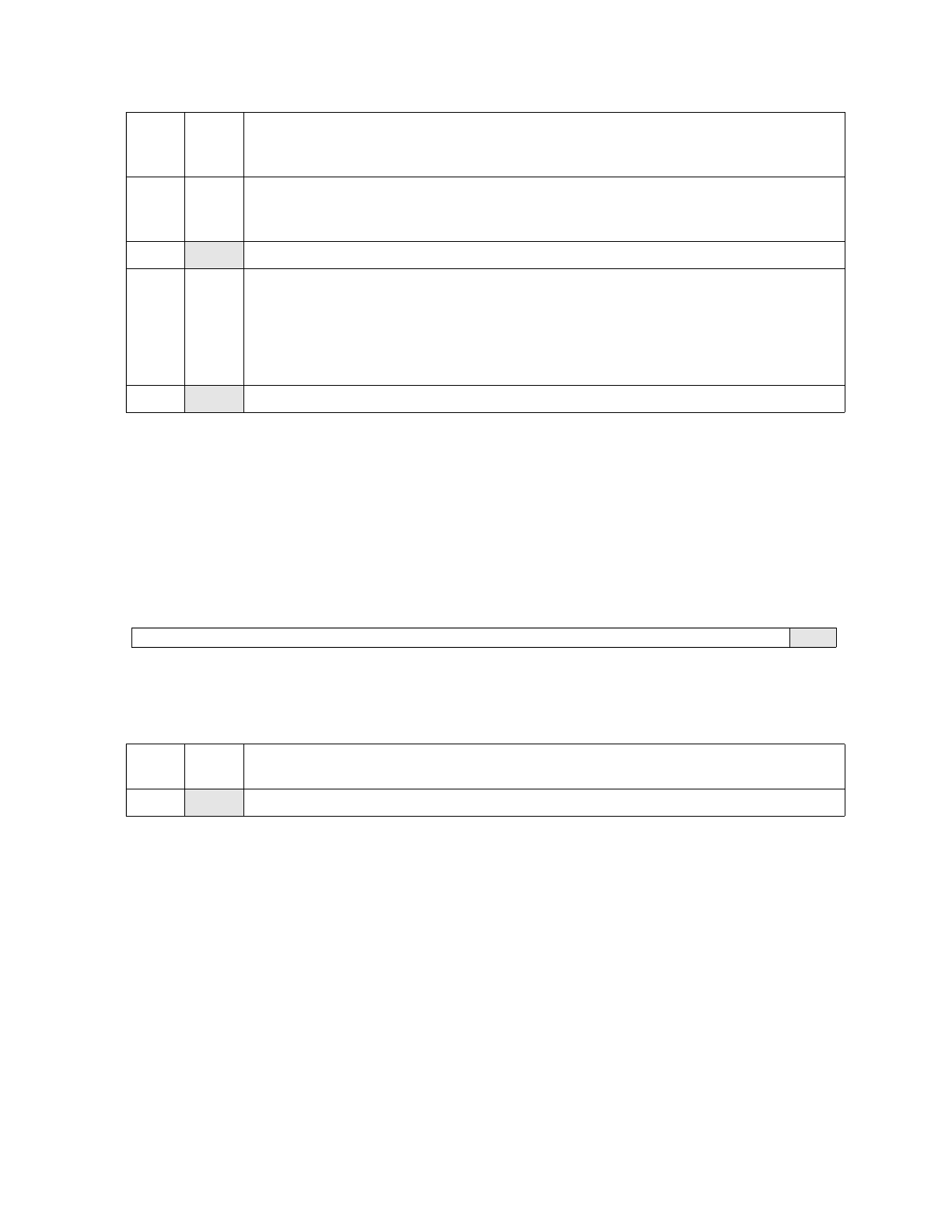

Figure 8-4. Instruction Address Compare Registers (IAC1–IAC4)

0:29 Instruction Address Compare word

address

Omit two low-order bits of complete

address.

30:31

Reserved

0 29 30 31