Instruction Summary A-41

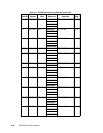

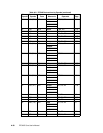

A.3 Instruction Formats

Instructions are four bytes long. Instruction addresses are always word-aligned.

Instruction bits 0 through 5 always contain the primary opcode. Many instructions have an extended

opcode in another field. Remaining instruction bits contain additional fields. All instruction fields

belong to one of the following categories:

• Defined

These instructions contain values, such as opcodes, that cannot be altered. The instruction format

diagrams specify the values of defined fields.

• Variable

These fields contain operands, such as GPR selectors and immediate values, that can vary from

execution to execution. The instruction format diagrams specify the operands in the variable fields.

• Reserved

Bits in reserved fields should be set to 0. In the instruction format diagrams, /, //, or /// indicate

reserved fields.

If any bit in a defined field does not contain the expected value, the instruction is illegal and an illegal

instruction exception occurs. If any bit in a reserved field does not contain 0, the instruction form is

invalid; its result is architecturally undefined. The PPC405 core executes all invalid instruction forms

without causing an illegal instruction exception.

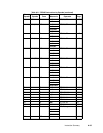

A.3.1 Instruction Fields

PPC405 instructions contain various combinations of the following fields, as indicated in the

instruction format diagrams that follow the field definitions. Numbers, enclosed in parentheses, that

follow the field names indicate bit positions; bit fields are indicated by starting and stopping bit

positions separated by colons.

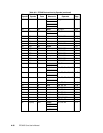

AA (30) Absolute address bit.

0 The immediate field represents an address relative to the current instruction

address (CIA). The effective address (EA) of the branch is either the sum of the LI

field sign-extended to 32 bits and the branch instruction address, or the sum of the

BD field sign-extended to 32 bits and the branch instruction address.

1 The immediate field represents an absolute address. The EA of the branch is

either the LI field or the BD field, sign-extended to 32 bits.

BA (11:15) Specifies a bit in the CR used as a source of a CR-logical instruction.

BB (16:20) Specifies a bit in the CR used as a source of a CR-logical instruction.

BD (16:29) An immediate field specifying a 14-bit signed twos complement branch displacement.

This field is concatenated on the right with 0b00 and sign-extended to 32 bits.

BF (6:8) Specifies a field in the CR used as a target in a compare or mcrf instruction.

BFA (11:13) Specifies a field in the CR used as a source in a mcrf instruction.

BI (11:15) Specifies a bit in the CR used as a source for the condition of a conditional branch

instruction.