Fixed-Point Interrupts and Exceptions 5-19

Executing an rfi instruction restores the program counter from SRR0 and the MSR from SRR1, and

execution resumes at the address in the program counter.

5.11 Alignment Interrupt

Alignment interrupts are caused by dcbz instructions to non-cachable or write-through storage,

misaligned dcread, lwarx, or stwx. instructions, or misaligned APU or FPU loads/stores. Table 5-10

summarizes the instructions and conditions causing alignment interrupts.

Execution of an instruction causing an alignment interrupt is prohibited from completing. SRR0 is

written with the address of that instruction and the current contents of the MSR are saved into SRR1.

The DEAR is written with the address that caused the alignment error. The MSR bits are written with

the values shown in Table 5-11 on page 5-19. The high-order 16 bits of the program counter are

written with the contents of the EVPR and the low-order 16 bits of the program counter are written

with 0x0600. Interrupt processing begins at the new address in the program counter.

Executing an rfi instruction restores the program counter from SRR0 and the MSR from SRR1, and

execution resumes at the address in the program counter

Alignment interrupts cannot be disabled. To avoid overwrites of SRR0 and SRR1 by alignment

interrupts that occur within a handler, interrupt handlers should save these registers as soon as

possible.

Table 5-9. Register Settings during External Interrupts

SRR0 Written with the address of the next sequential instruction

SRR1 Written with the contents of the MSR

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged

PC EVPR[0:15] || 0x0500

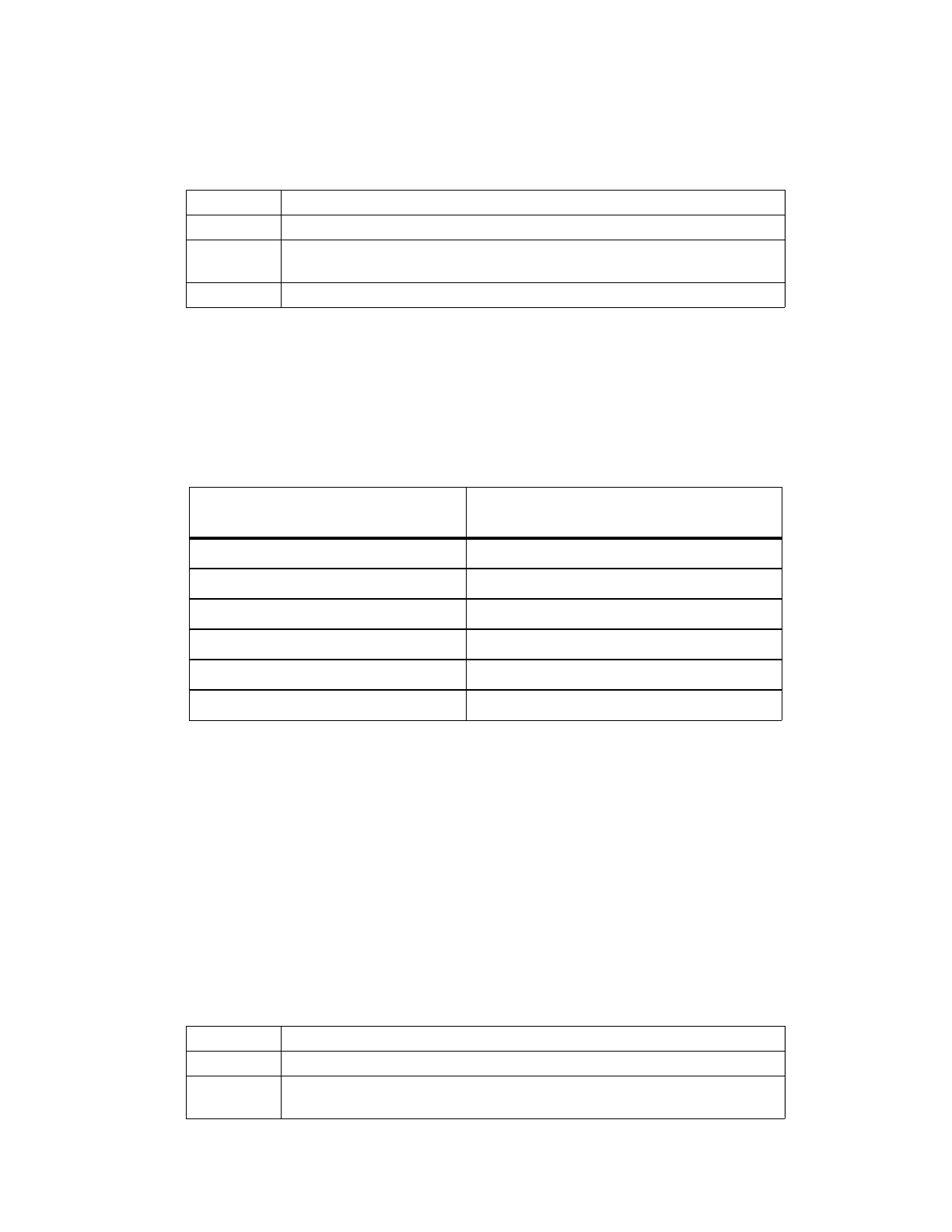

Table 5-10. Alignment Interrupt Summary

Instructions Causing Alignment

Interrupts Conditions

dcbz EA in non-cachable or write-through storage

dcread, lwarx, stwcx. EA not word-aligned

APU or FPU load/store halfword EA not halfword-aligned

APU or FPU load/store word EA not word-aligned

APU or FPU load/store doubleword EA not word-aligned

APU load/store quadword EA not quadword-aligned

Table 5-11. Register Settings during Alignment Interrupts

SRR0 Written with the address of the instruction causing the alignment interrupt

SRR1 Written with the contents of the MSR

MSR AP, APE, WE, EE, PR, FP, FE0, DWE, FE1, IR, DR ← 0

CE, ME, DE ← unchanged