Initialization 3-3

3.1.2 Contents of Special Purpose Registers after Reset

In general, the contents of Special Purpose Registers (SPRs) are undefined after a core, chip, or

system reset. Some SPRs retain the contents they had before a reset occurred.

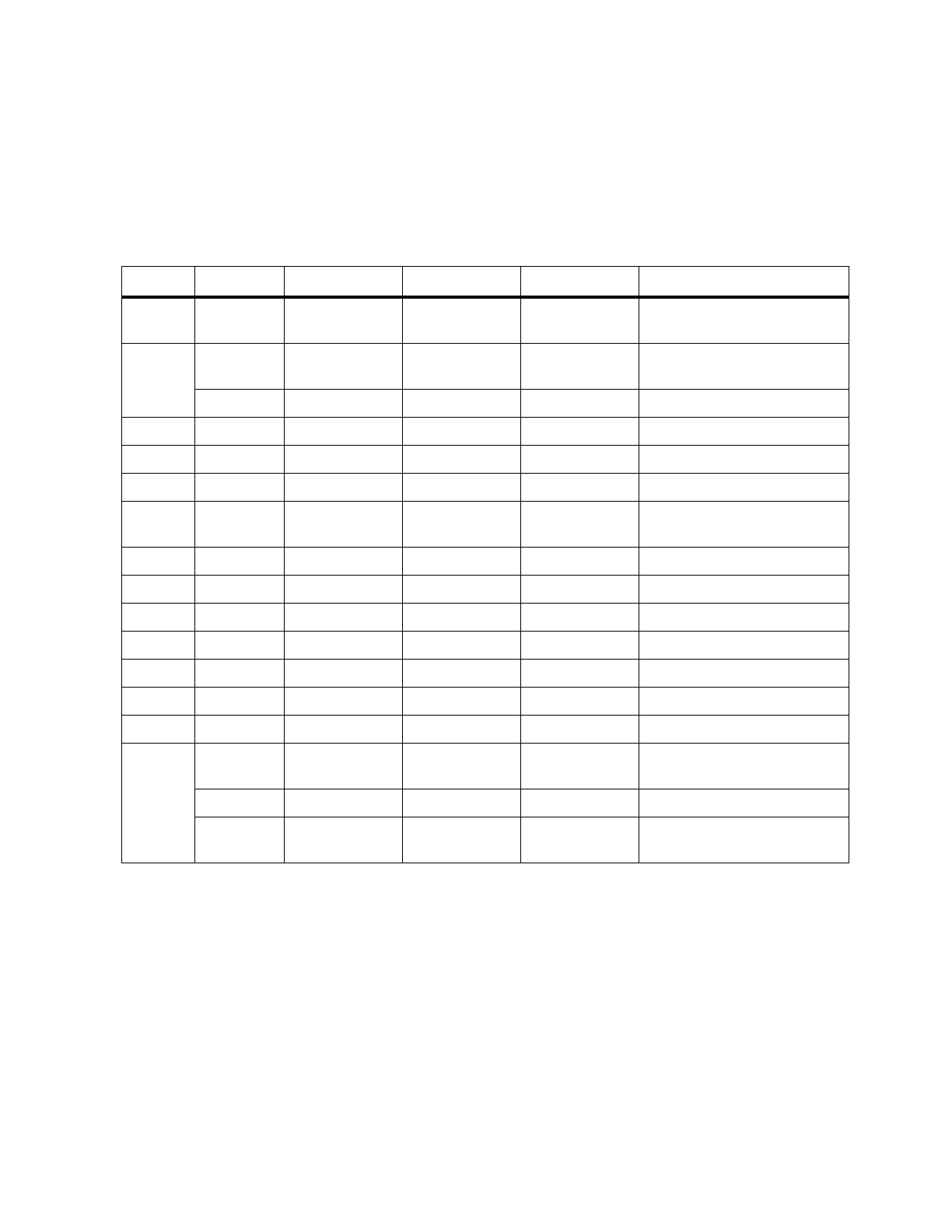

Table 3-2 shows the contents of SPRs that are defined or unchanged after core, chip, and system

resets.

3.2 PPC405 Initial Processor Sequencing

After any reset, the processor core fetches the word at address 0xFFFFFFFC and attempts to

execute it. The instruction at 0xFFFFFFFC is typically a branch to initialization code. Unless the

instruction at 0xFFFFFFFC is an unconditional branch, fetching can wrap to address 0x00000000

and attempt to execute the instruction at this location.

Table 3-2. SPR Contents After Reset

Register Bits/Fields Core Reset Chip Reset System Reset Comment

CCR0 0:31 0x00700000 0x00700000 0x00700000 Sets ICU and DCU PLB

priorities

DBCR0 EDM 0 0 0 External debug mode

disabled

RST 00 00 00 No reset action.

DBCR1 0:31 0x00000000 0x00000000 0x00000000 Data compares disabled

DBSR MRR 01 10 11 Most recent reset

DCCR S0:S31 0x00000000 0x00000000 0x00000000 Data cache disabled

DCWR W0:W31 0x00000000 0x00000000 0x00000000 Data cache write-through

disabled

ESR 0:31 0x00000000 0x00000000 0x00000000 No exception syndromes

ICCR S0:S31 0x00000000 0x00000000 0x00000000 Instruction cache disabled

PVR 0:31 Processor version

SGR G0:G31 0xFFFFFFFF 0xFFFFFFFF 0xFFFFFFFF Storage is guarded

SLER S0:S31 0x00000000 0x00000000 0x00000000 Storage is big endian

SU0R K0:K31 0x00000000 0x00000000 0x00000000 Storage is uncompressed

TCR WRC 00 00 00 Watchdog timer reset disabled

TSR WRS Copy of

TCR[WRC]

Copy of

TCR[WRC]

Copy of

TCR[WRC]

Watchdog reset status

PIS Undefined Undefined Undefined After POR

FIS Unchanged Unchanged Unchanged If reset not caused by

watchdog timer