2-36 PPC405 Core User’s Manual

stw Store to peripheral

sync Wait for store to actually complete

mtdcr Reconfigure device

The eieio instruction guarantees the order of storage accesses. All storage accesses that precede

eieio complete before any storage accesses that follow the instruction, as in the following example:

stb X Store to peripheral, address X; this resets a status bit in the device

eieio Guarantee stb X completes before next instruction

lbz Y Load from peripheral, address Y; this is the status register updated by stb X.

eieio was necessary, because the read and write addresses are different, but

affect each other

The PPC405 core implements both sync and eieio identically, in the manner described above for

sync. In the PowerPC Architecture, sync can function across all processors in a multiprocessor

environment; eieio functions only within its executing processor. The PPC405 does not provide

hardware support for multiprocessor memory coherency, so sync does not guarantee memory

ordering across multiple processors.

2.11 Instruction Set

The PPC405 instruction set contains instructions defined in the PowerPC Architecture and

instructions specific to the IBM PowerPC 400 family of embedded processors.

Chapter 9, “Instruction Set,” contains detailed descriptions of each instruction.

Appendix A, “Instruction Summary,” alphabetically lists each instruction and extended mnemonic and

provides a short-form description. Appendix B, “Instructions by Category,” provides short-form

descriptions of instructions, grouped by the instruction categories listed in Table 2-10, “PPC405

Instruction Set Summary,” on page 2-36.

Table 2-10 summarizes the PPC405 instruction set functions by categories. Instructions within each

category are described in subsequent sections.

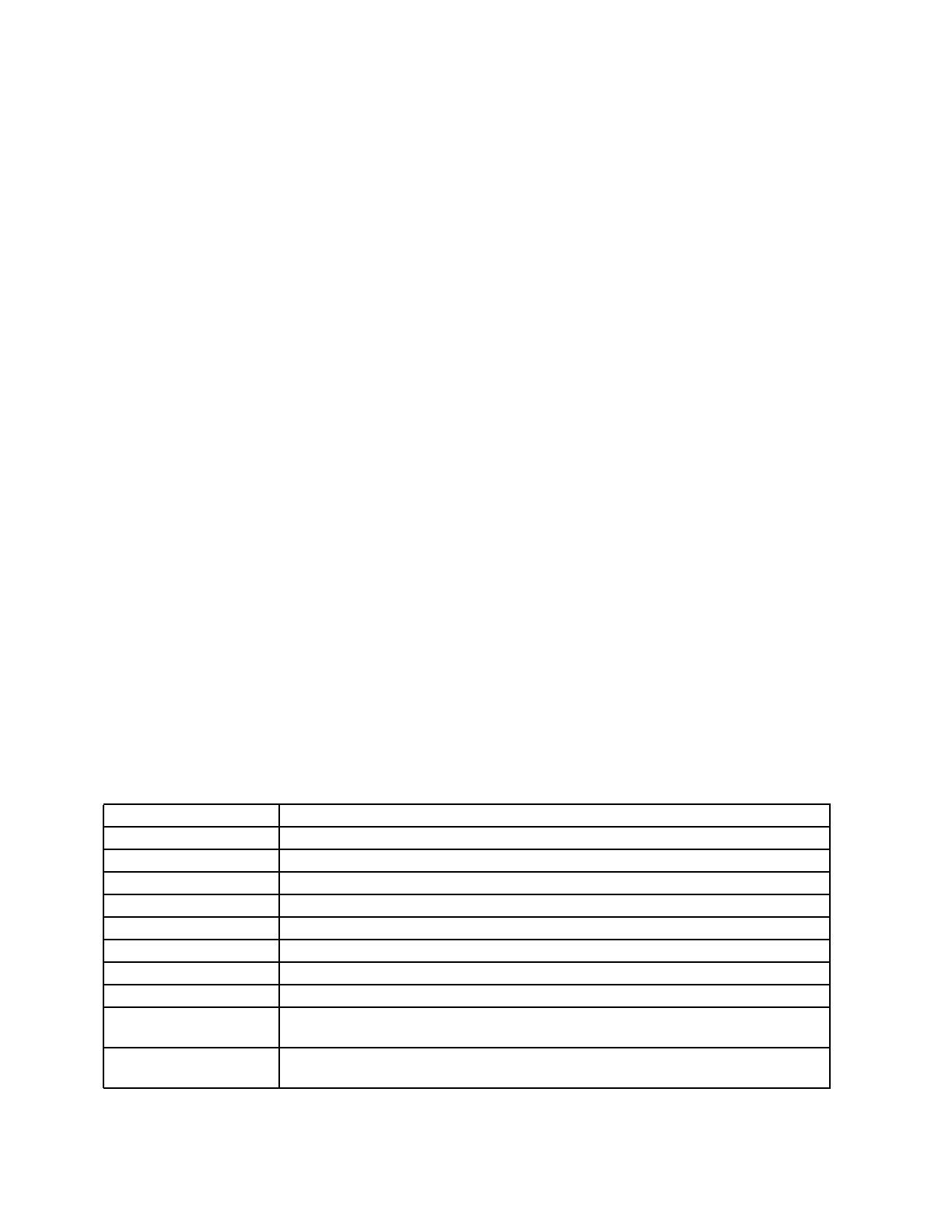

Table 2-10. PPC405 Instruction Set Summary

Storage Reference load, store

Arithmetic add, subtract, negate, multiply, multiply-accumulate, multiply halfword, divide

Logical and, andc, or, orc, xor, nand, nor, xnor, sign extension, count leading zeros

Comparison compare, compare logical, compare immediate

Branch branch, branch conditional, branch to LR, branch to CTR

CR Logical crand, crandc, cror, crorc, crnand, crnor, crxor, crxnor, move CR field

Rotate rotate and insert, rotate and mask, shift left, shift right

Shift shift left, shift right, shift right algebraic

Cache Management invalidate, touch, zero, flush, store, read

Interrupt Control write to external interrupt enable bit, move to/from MSR, return from interrupt,

return from critical interrupt

Processor Management system call, synchronize, trap, move to/from DCRs, move to/from SPRs, move

to/from CR