Vol. 3 4-3

PAGING

linear addresses larger than 32 bits, 32-bit paging and PAE paging translate 32-bit

linear addresses.

Because it is used only if IA32_EFER.LME = 1, IA-32e paging is used only in IA-32e

mode. (In fact, it is the use of IA-32e paging that defines IA-32e mode.) IA-32e

mode has two sub-modes:

• Compatibility mode. This mode uses only 32-bit linear addresses. IA-32e paging

treats bits 47:32 of such an address as all 0.

• 64-bit mode. While this mode produces 64-bit linear addresses, the processor

ensures that bits 63:47 of such an address are identical.

1

IA-32e paging does not

use bits 63:48 of such addresses.

4.1.2 Paging-Mode Enabling

If CR0.PG = 1, a logical processor is in one of three paging modes, depending on the

values of CR4.PAE and IA32_EFER.LME. Figure 4-1 illustrates how software can

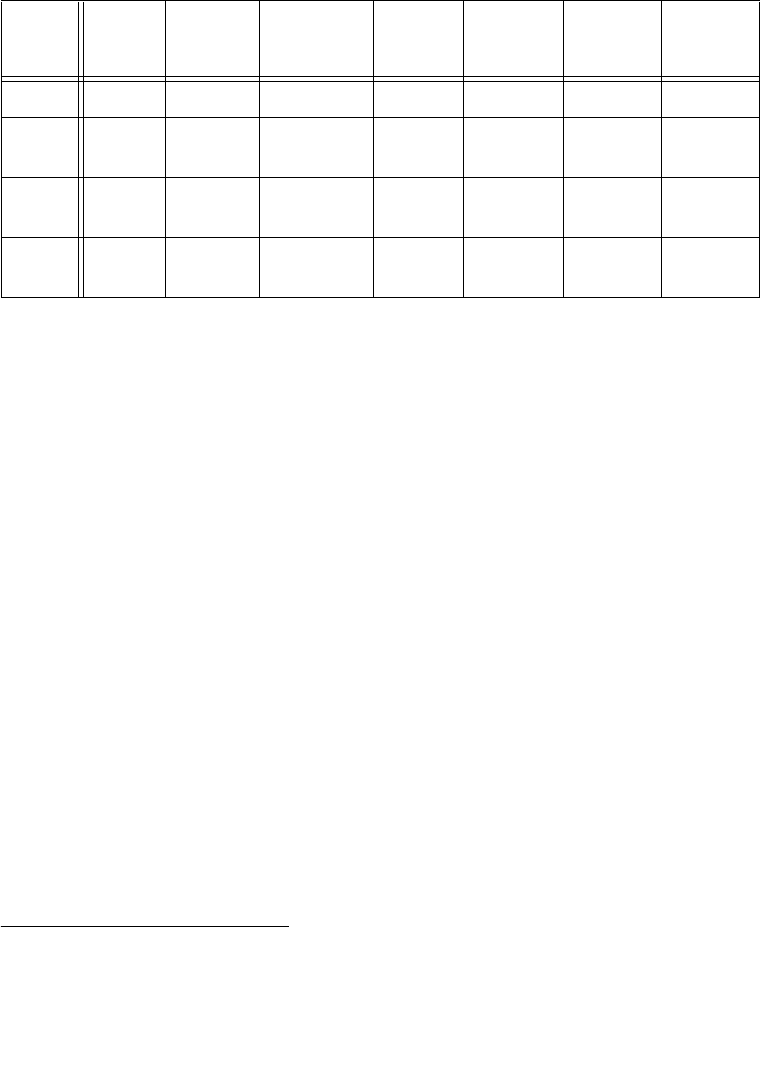

Table 4-1. Properties of Different Paging Modes

Paging

Mode

CR0.PG CR4.PAE

LME in

IA32_EFER

Linear-

Address

Width

Physical-

Address

Width

1

Page

Size(s)

Supports

Execute-

Disable?

None 0 N/A N/A 32 32 N/A No

32-bit 1 0 0

2

32 Up to 40

3

4-KByte

4-MByte

4

No

PAE 1 1 0 32 Up to 52

4-KByte

2-MByte

Yes

5

IA-32e 1 1 2 48 Up to 52

4-KByte

2-MByte

Yes

5

NOTES:

1. The physical-address width is always bounded by MAXPHYADDR; see Section 4.1.4.

2. The processor ensures that IA32_EFER.LME must be 0 if CR0.PG = 1 and CR4.PAE = 0.

3. 32-bit paging supports physical-address widths of more than 32 bits only for 4-MByte pages and

only if the PSE-36 mechanism is supported; see Section 4.1.4 and Section 4.3.

4. 4-MByte pages are used with 32-bit paging only if CR4.PSE = 1; see Section 4.3.

5. Execute-disable access rights are applied only if IA32_EFER.NXE = 1; see Section 4.6.

1. Such an address is called canonical. Use of a non-canonical linear address in 64-bit mode pro-

duces a general-protection exception (#GP(0)); the processor does not attempt to translate non-

canonical linear addresses using IA-32e paging.